- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi,

I got below questions from my customer about Ethernet timings.

Please answer them.

Q1)

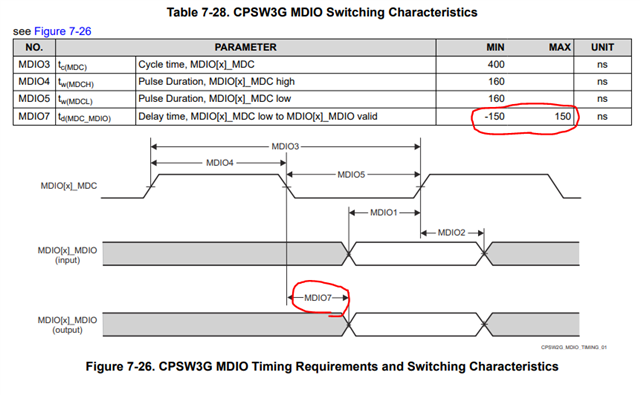

In datasheet Table 7-28 and Figure 7-26, parameter MDIO7 is min.-150ns and max.150nsec.

If this value is 0ns, setup and hold time at PHY side is also 0n and it cannot meet min. 10nsec which is IEEE 802.3 standard.

Why?

Q2)

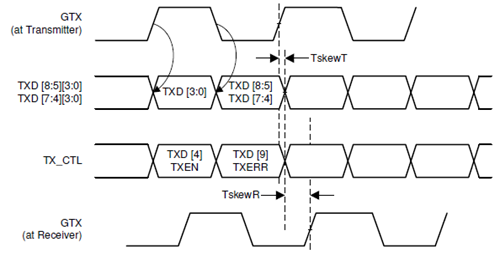

Datasheet Table 7-33 to 7-37 provide RGMII timings, but it seems below parameters are not shown.

#1 TskewT: Data to Clock output Skew(at transmitter)

#2 TskewR: Data to Clock input Skew(at Receiver)

#3 Duty Cycle(for 1000BASE)

#4 Rise Time(20-80%)

#5 Fall Time(80-20%)

Can you provide these parameters (min/typ/max)?

Thanks and regards,

Koichiro Tashiro

Question 1: The MDIO7 min/max values need to be updated in the AM62x datasheet. We found this error since the last datasheet revision. The values will be updated in the next revision of the datasheet. The new min value will be -10ns and the new max value will be 10ns. You can see the update has already been applied to the AM62Ax datasheet.

Question 2, #1: The clock to data skew associated with the AM62x output is defined in the table titled "RGMII[x]_TD[3:0] and RGMII[x]_TX_CTL Switching Characteristics – RGMII Mode". The skew is presented as output setup time and output hold time to be consistent with how this requirement is defined in the RGMII specification, where the data is valid for a minimum of 1.2ns before the clock and remains valid for a minimum of 1.2ns after the clock.

Question 2, #2: The clock to data skew associated with the AM62x output is defined in the table titled "RGMII[x]_RD[3:0], and RGMII[x]_RX_CTL Timing Requirements – RGMII Mode". The skew allowed to capture valid data is presented as setup time and hold time, where the data is expected to be valid for a minimum of 1.0ns before the clock and remain valid for a minimum of 1.0ns after the clock.

Question 2, #3: The clock duty cycle requirements of the receiver and the clock duty cycle characteristics of the transmitter are defined by the min/max pulse duration values when compared to the expected clock period. See the tables titled "RGMII[x]_RXC Timing Requirements – RGMII Mode" and "RGMII[x]_TXC Switching Characteristics – RGMII Mode". For example, the clock period will be 8ns when operating at the 1000 Mbps and the min/max pulse duration is defined to be 3.6ns/4.4ns. This represents a worst-case duty cycle of 45%/55%, which matches the limits defined in the RGMII specification.

Question 2, #4 and #5: The customer must use the device IBIS models along with their actual PCB loading to determine rise/fall times.