Other Parts Discussed in Thread: AM5748

Hi Team,

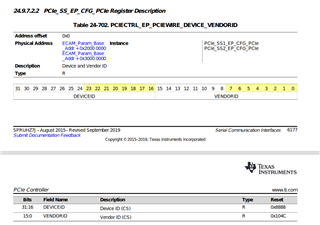

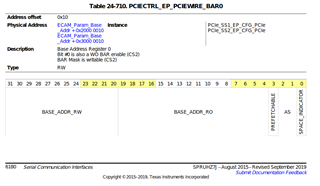

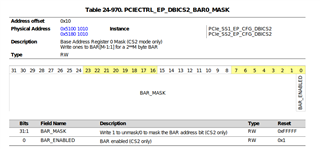

In our system we're using two Sitara AM5706 processors as PCIe end points and intel SBC as root complex, problem is since both end points are having same PCI vendor and device IDs we're unable to communicate properly from root complex. So, could you please let us know that is there a way that we can change Vendor or Device ID of PCI in AM5706 processor.

Regards,

Sarath