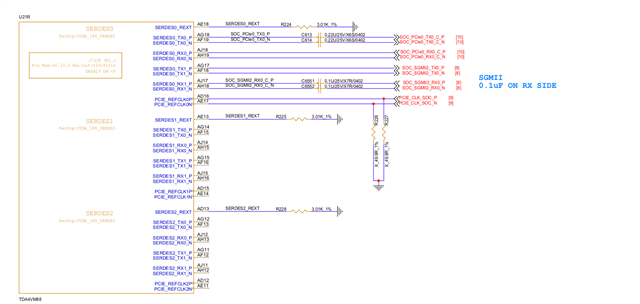

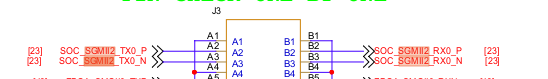

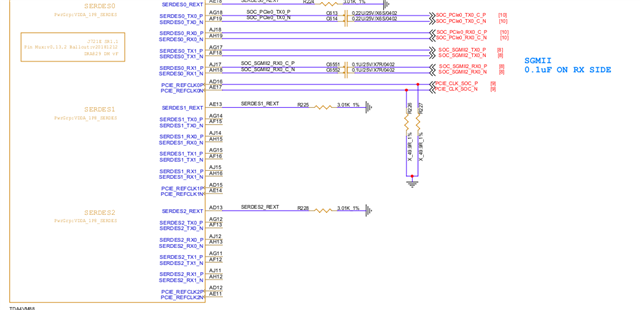

I used TDA4VM (serdes0 lane1) to connect a externel switch by MAC-to-MAC SGMII mode. My SDK version is 08.04. My code changes as follow:

Linux DTS:

diff --git a/linux/board-support/linux-5.10.120+gitAUTOINC+95b90aa828-g95b90aa828/arch/arm64/boot/dts/ti/k3-j721e-common-proc-board.dts b/linux/board-support/linux-5.10.120+gitAUTOINC+95b90aa828-g95b90aa828/arch/arm64/boot/dts/ti/k3-j721e-common-proc-board.dts

index ab3fe1ee4..87a0bafa3 100644

--- a/linux/board-support/linux-5.10.120+gitAUTOINC+95b90aa828-g95b90aa828/arch/arm64/boot/dts/ti/k3-j721e-common-proc-board.dts

+++ b/linux/board-support/linux-5.10.120+gitAUTOINC+95b90aa828-g95b90aa828/arch/arm64/boot/dts/ti/k3-j721e-common-proc-board.dts

@@ -517,8 +517,7 @@ &usb_serdes_mux {

};

diff --git a/linux/board-support/linux-5.10.120+gitAUTOINC+95b90aa828-g95b90aa828/arch/arm64/boot/dts/ti/k3-j721e-common-proc-board.dts b/linux/board-support/linux-5.10.120+gitAUTOINC+9

5b90aa828-g95b90aa828/arch/arm64/boot/dts/ti/k3-j721e-common-proc-board.dts

index ab3fe1ee4..87a0bafa3 100644

--- a/linux/board-support/linux-5.10.120+gitAUTOINC+95b90aa828-g95b90aa828/arch/arm64/boot/dts/ti/k3-j721e-common-proc-board.dts

+++ b/linux/board-support/linux-5.10.120+gitAUTOINC+95b90aa828-g95b90aa828/arch/arm64/boot/dts/ti/k3-j721e-common-proc-board.dts

@@ -517,8 +517,7 @@ &usb_serdes_mux {

};

&serdes_ln_ctrl {

- idle-states = <J721E_SERDES0_LANE0_PCIE0_LANE0>, <J721E_SERDES0_LANE1_QSGMII_LANE2>,

- <J721E_SERDES1_LANE0_PCIE1_LANE0>, <J721E_SERDES1_LANE1_PCIE1_LANE1>,

+ idle-states = <J721E_SERDES1_LANE0_PCIE1_LANE0>, <J721E_SERDES1_LANE1_PCIE1_LANE1>,

<J721E_SERDES2_LANE0_PCIE2_LANE0>, <J721E_SERDES2_LANE1_PCIE2_LANE1>,

<J721E_SERDES3_LANE0_USB3_0_SWAP>, <J721E_SERDES3_LANE1_USB3_0>,

<J721E_SERDES4_LANE0_EDP_LANE0>, <J721E_SERDES4_LANE1_EDP_LANE1>,

@@ -991,9 +990,6 @@ &cmn_refclk1 {

};

&serdes0 {

- assigned-clocks = <&serdes0 CDNS_SIERRA_PLL_CMNLC>, <&serdes0 CDNS_SIERRA_PLL_CMNLC1>;

- assigned-clock-parents = <&wiz0_pll1_refclk>, <&wiz0_pll1_refclk>;

-

serdes0_pcie_link: phy@0 {

reg = <0>;

cdns,num-lanes = <1>;

@@ -1001,15 +997,6 @@ serdes0_pcie_link: phy@0 {

cdns,phy-type = <PHY_TYPE_PCIE>;

resets = <&serdes_wiz0 1>;

};

-

- serdes0_qsgmii_link: phy@1 {

- reg = <1>;

- cdns,num-lanes = <1>;

- #phy-cells = <0>;

- cdns,phy-type = <PHY_TYPE_QSGMII>;

- resets = <&serdes_wiz0 2>;

- };

-

};

&serdes1 {

@@ -1038,15 +1025,6 @@ serdes2_pcie_link: phy@0 {

};

};

-&cpsw0 {

- /*

- * Disable cpsw0 since cpsw9g_virt_mac is the default Ethernet

- * controller. cpsw0 is enabled with overlay for native

- * Ethernet driver support.

- */

- status = "disabled";

-};

-

&pcie0_rc {

reset-gpios = <&exp1 6 GPIO_ACTIVE_HIGH>;

phys = <&serdes0_pcie_link>;

@@ -1081,6 +1059,7 @@ &pcie0_ep {

device-ids = /bits/ 16 <0xb00d>;

msi_interrupts = /bits/ 8 <2>;

msix_interrupts = /bits/ 16 <2>;

+ status = "disabled";

};

&pcie1_ep {

@@ -1225,3 +1204,7 @@ &main_ehrpwm4 {

&main_ehrpwm5 {

status = "disabled";

};

+

+&serdes_wiz0 {

+ status = "disabled";

+};

diff --git a/linux/board-support/linux-5.10.120+gitAUTOINC+95b90aa828-g95b90aa828/arch/arm64/boot/dts/ti/k3-j721e-main.dtsi b/linux/board-support/linux-5.10.120+gitAUTOINC+95b90aa828-g95b90aa828/arch/arm64/boot/dts/ti/k3-j721e-main.dtsi

index 59b1042c4..432526ff1 100644

--- a/linux/board-support/linux-5.10.120+gitAUTOINC+95b90aa828-g95b90aa828/arch/arm64/boot/dts/ti/k3-j721e-main.dtsi

+++ b/linux/board-support/linux-5.10.120+gitAUTOINC+95b90aa828-g95b90aa828/arch/arm64/boot/dts/ti/k3-j721e-main.dtsi

@@ -46,27 +46,18 @@ serdes_ln_ctrl: mux@4080 {

compatible = "mmio-mux";

reg = <0x00004080 0x50>;

#mux-control-cells = <1>;

- mux-reg-masks = <0x4080 0x3>, <0x4084 0x3>, /* SERDES0 lane0/1 select */

- <0x4090 0x3>, <0x4094 0x3>, /* SERDES1 lane0/1 select */

+ mux-reg-masks = <0x4090 0x3>, <0x4094 0x3>, /* SERDES1 lane0/1 select */

<0x40a0 0x3>, <0x40a4 0x3>, /* SERDES2 lane0/1 select */

<0x40b0 0x3>, <0x40b4 0x3>, /* SERDES3 lane0/1 select */

<0x40c0 0x3>, <0x40c4 0x3>, <0x40c8 0x3>, <0x40cc 0x3>;

/* SERDES4 lane0/1/2/3 select */

- idle-states = <J721E_SERDES0_LANE0_PCIE0_LANE0>, <J721E_SERDES0_LANE1_PCIE0_LANE1>,

- <J721E_SERDES1_LANE0_PCIE1_LANE0>, <J721E_SERDES1_LANE1_PCIE1_LANE1>,

+ idle-states = <J721E_SERDES1_LANE0_PCIE1_LANE0>, <J721E_SERDES1_LANE1_PCIE1_LANE1>,

<J721E_SERDES2_LANE0_PCIE2_LANE0>, <J721E_SERDES2_LANE1_PCIE2_LANE1>,

<MUX_IDLE_AS_IS>, <J721E_SERDES3_LANE1_USB3_0>,

<J721E_SERDES4_LANE0_EDP_LANE0>, <J721E_SERDES4_LANE1_EDP_LANE1>,

<J721E_SERDES4_LANE2_EDP_LANE2>, <J721E_SERDES4_LANE3_EDP_LANE3>;

};

- cpsw0_phy_gmii_sel: phy@4044 {

- compatible = "ti,j721e-cpsw9g-phy-gmii-sel";

- ti,qsgmii-main-ports = <2>, <1>;

- reg = <0x4044 0x20>;

- #phy-cells = <1>;

- };

-

usb_serdes_mux: mux-controller@4000 {

compatible = "mmio-mux";

#mux-control-cells = <1>;

@@ -390,104 +381,6 @@ cpts@310d0000 {

};

};

- cpsw0: ethernet@c000000 {

- compatible = "ti,j721e-cpswxg-nuss";

- #address-cells = <2>;

- #size-cells = <2>;

- reg = <0x00 0xc000000 0x00 0x200000>;

- reg-names = "cpsw_nuss";

- ranges = <0x00 0x00 0x00 0xc000000 0x00 0x200000>;

- clocks = <&k3_clks 19 89>;

- clock-names = "fck";

- power-domains = <&k3_pds 19 TI_SCI_PD_EXCLUSIVE>;

-

- dmas = <&main_udmap 0xca00>,

- <&main_udmap 0xca01>,

- <&main_udmap 0xca02>,

- <&main_udmap 0xca03>,

- <&main_udmap 0xca04>,

- <&main_udmap 0xca05>,

- <&main_udmap 0xca06>,

- <&main_udmap 0xca07>,

- <&main_udmap 0x4a00>;

- dma-names = "tx0", "tx1", "tx2", "tx3",

- "tx4", "tx5", "tx6", "tx7",

- "rx";

-

- ethernet-ports {

- #address-cells = <1>;

- #size-cells = <0>;

- cpsw0_port1: port@1 {

- reg = <1>;

- ti,mac-only;

- label = "port1";

- };

-

- cpsw0_port2: port@2 {

- reg = <2>;

- ti,mac-only;

- label = "port2";

- };

-

- cpsw0_port3: port@3 {

- reg = <3>;

- ti,mac-only;

- label = "port3";

- };

-

- cpsw0_port4: port@4 {

- reg = <4>;

- ti,mac-only;

- label = "port4";

- };

-

- cpsw0_port5: port@5 {

- reg = <5>;

- ti,mac-only;

- label = "port5";

- };

-

- cpsw0_port6: port@6 {

- reg = <6>;

- ti,mac-only;

- label = "port6";

- };

-

- cpsw0_port7: port@7 {

- reg = <7>;

- ti,mac-only;

- label = "port7";

- };

-

- cpsw0_port8: port@8 {

- reg = <8>;

- ti,mac-only;

- label = "port8";

- };

- };

-

- cpsw9g_mdio: mdio@f00 {

- compatible = "ti,cpsw-mdio","ti,davinci_mdio";

- reg = <0x00 0xf00 0x00 0x100>;

- #address-cells = <1>;

- #size-cells = <0>;

- clocks = <&k3_clks 19 89>;

- clock-names = "fck";

- bus_freq = <1000000>;

- };

-

- cpts@3d000 {

- compatible = "ti,j721e-cpts";

- reg = <0x00 0x3d000 0x00 0x400>;

- clocks = <&k3_clks 19 16>;

- clock-names = "cpts";

- interrupts-extended = <&gic500 GIC_SPI 16 IRQ_TYPE_LEVEL_HIGH>;

- interrupt-names = "cpts";

- ti,cpts-ext-ts-inputs = <4>;

- ti,cpts-periodic-outputs = <2>;

- };

- };

-

main_crypto: crypto@4e00000 {

compatible = "ti,j721e-sa2ul";

reg = <0x0 0x4e00000 0x0 0x1200>;

vision_app:

enable_ethfw

diff --git a/rtos/vision_apps/utils/ethfw/src/app_ethfw_freertos.c b/rtos/vision_apps/utils/ethfw/src/app_ethfw_freertos.c

index cc484978a..33f3d7a5f 100644

--- a/rtos/vision_apps/utils/ethfw/src/app_ethfw_freertos.c

+++ b/rtos/vision_apps/utils/ethfw/src/app_ethfw_freertos.c

@@ -135,9 +135,6 @@ static Enet_MacPort gEthAppPorts[] =

ENET_MAC_PORT_8, /* RGMII */

#if defined(ENABLE_QSGMII_PORTS)

ENET_MAC_PORT_2, /* QSGMII main */

- ENET_MAC_PORT_5, /* QSGMII sub */

- ENET_MAC_PORT_6, /* QSGMII sub */

- ENET_MAC_PORT_7, /* QSGMII sub */

#endif

#elif defined(SOC_J784S4)

ENET_MAC_PORT_1, /* QSGMII main */

@@ -310,7 +307,7 @@ int32_t appEthFwInit()

#if defined(SOC_J721E)

flags |= ETHFW_BOARD_GESI_ENABLE;

#if defined(ENABLE_QSGMII_PORTS)

- flags |= ETHFW_BOARD_QENET_ENABLE;

+ flags |= ETHFW_BOARD_ENET_BRIDGE_ENABLE;

#endif

#elif defined(SOC_J784S4)

flags |= (ETHFW_BOARD_QENET_ENABLE | ETHFW_BOARD_SERDES_CONFIG);

PDK

diff --git a/rtos/pdk_jacinto_08_04_00_21/packages/ti/board/src/j721e_evm/board_ethernet_config.c b/rtos/pdk_jacinto_08_04_00_21/packages/ti/board/src/j721e_evm/board_ethernet_config.c

index 575b2e2db..cc8baba03 100755

--- a/rtos/pdk_jacinto_08_04_00_21/packages/ti/board/src/j721e_evm/board_ethernet_config.c

+++ b/rtos/pdk_jacinto_08_04_00_21/packages/ti/board/src/j721e_evm/board_ethernet_config.c

@@ -720,11 +720,11 @@ Board_STATUS Board_ethConfigCpsw9g(void)

{

if (1U == portNum)

{

- status = Board_cpsw9gEthConfig(portNum, QSGMII);

+ status = Board_cpsw9gEthConfig(portNum, SGMII);^M

}

else

{

- status = Board_cpsw9gEthConfig(portNum, QSGMII_SUB);

+ status = Board_cpsw9gEthConfig(portNum, SGMII);^M

}

}

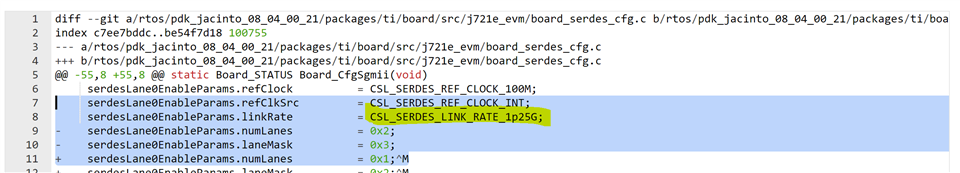

diff --git a/rtos/pdk_jacinto_08_04_00_21/packages/ti/board/src/j721e_evm/board_serdes_cfg.c b/rtos/pdk_jacinto_08_04_00_21/packages/ti/board/src/j721e_evm/board_serdes_cfg.c

index c7ee7bddc..be54f7d18 100755

--- a/rtos/pdk_jacinto_08_04_00_21/packages/ti/board/src/j721e_evm/board_serdes_cfg.c

+++ b/rtos/pdk_jacinto_08_04_00_21/packages/ti/board/src/j721e_evm/board_serdes_cfg.c

@@ -55,8 +55,8 @@ static Board_STATUS Board_CfgSgmii(void)

serdesLane0EnableParams.refClock = CSL_SERDES_REF_CLOCK_100M;

serdesLane0EnableParams.refClkSrc = CSL_SERDES_REF_CLOCK_INT;

serdesLane0EnableParams.linkRate = CSL_SERDES_LINK_RATE_1p25G;

- serdesLane0EnableParams.numLanes = 0x2;

- serdesLane0EnableParams.laneMask = 0x3;

+ serdesLane0EnableParams.numLanes = 0x1;^M

+ serdesLane0EnableParams.laneMask = 0x2;^M

serdesLane0EnableParams.SSC_mode = CSL_SERDES_NO_SSC;

serdesLane0EnableParams.phyType = CSL_SERDES_PHY_TYPE_SGMII;

serdesLane0EnableParams.operatingMode = CSL_SERDES_FUNCTIONAL_MODE;

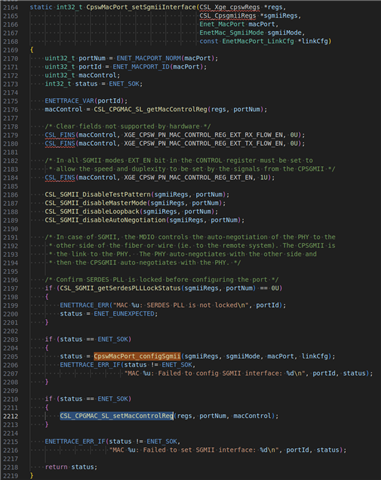

diff --git a/rtos/pdk_jacinto_08_04_00_21/packages/ti/drv/enet/src/mod/cpsw_macport.c b/rtos/pdk_jacinto_08_04_00_21/packages/ti/drv/enet/src/mod/cpsw_macport.c

index 1fb23b830..7a0c5640b 100755

--- a/rtos/pdk_jacinto_08_04_00_21/packages/ti/drv/enet/src/mod/cpsw_macport.c

+++ b/rtos/pdk_jacinto_08_04_00_21/packages/ti/drv/enet/src/mod/cpsw_macport.c

@@ -2304,6 +2304,7 @@ static int32_t CpswMacPort_configSgmii(CSL_CpsgmiiRegs *sgmiiRegs,

do

{

CSL_SGMII_getStatus(sgmiiRegs, portNum, &sgmiiStatus);

+ sgmiiStatus.bIsLinkUp = 1;

}

while (sgmiiStatus.bIsLinkUp != 1U);

EthFw

diff --git a/rtos/ethfw/utils/board/src/j721e/board_j721e_evm.c b/rtos/ethfw/utils/board/src/j721e/board_j721e_evm.c

index d547a8773..e6ec4f081 100755

--- a/rtos/ethfw/utils/board/src/j721e/board_j721e_evm.c

+++ b/rtos/ethfw/utils/board/src/j721e/board_j721e_evm.c

@@ -367,7 +367,7 @@ static EthFwBoard_MacPortCfg gEthFw_enetBridgeMacPortCfg =

.extendedCfg = NULL,

.extendedCfgSize = 0U,

},

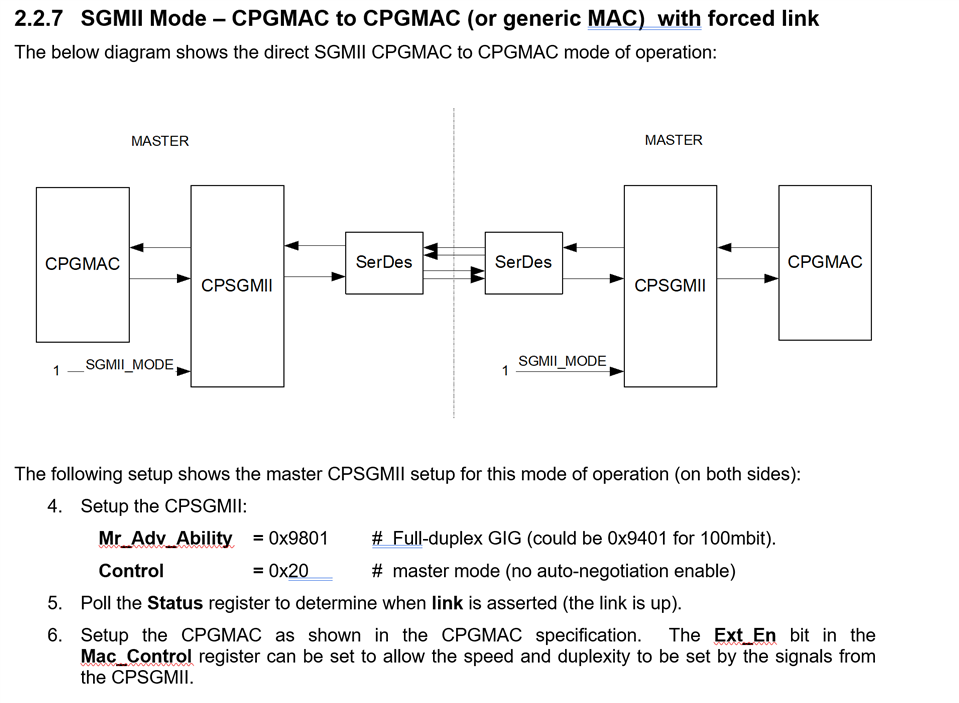

- .sgmiiMode = ENET_MAC_SGMIIMODE_SGMII_AUTONEG_MASTER,

+ .sgmiiMode = ENET_MAC_SGMIIMODE_SGMII_FORCEDLINK,

.linkCfg = { ENET_SPEED_1GBIT, ENET_DUPLEX_FULL },

};

@@ -659,13 +659,13 @@ static void EthFwBoard_configSerdesBridge(void)

{

Board_STATUS boardStatus;

- if (gEthFwBoard.serdesAllowed)

+ //if (gEthFwBoard.serdesAllowed)

{

/* Configure SerDes clocks */

EthFwBoard_configSierra0Clks();

/* Configure SerDes for XAUI functionality */

- boardStatus = Board_serdesCfgXaui();

+ boardStatus = Board_serdesCfgSgmii();

EnetAppUtils_assert(boardStatus == BOARD_SOK);

}

}