Hi,Ti

when debugging PCIe_M.2 on our custom board, we can not found ssd. So we modify TDA4VM EVM to the same as our board, and test ssd on TDA4VM EVM again, it failed. Before modified the TDA4VM EVM can found SSD.the log as fellows:

root@j7-evm:~# dmesg |grep pcie [ 1.206578] j721e-pcie 2900000.pcie: host bridge /bus@100000/pcie@2900000 ranges: [ 1.214252] j721e-pcie 2900000.pcie: IO 0x0010001000..0x0010010fff -> 0x0010001000 [ 1.222529] j721e-pcie 2900000.pcie: MEM 0x0010011000..0x0017ffffff -> 0x0010011000 [ 1.230805] j721e-pcie 2900000.pcie: IB MEM 0x0000000000..0xffffffffffff -> 0x0000000000 [ 2.250167] j721e-pcie 2900000.pcie: PCI host bridge to bus 0000:00 [ 2.353792] pcieport 0000:00:00.0: PME: Signaling with IRQ 68 [ 2.360173] j721e-pcie 2910000.pcie: host bridge /bus@100000/pcie@2910000 ranges: [ 2.367840] j721e-pcie 2910000.pcie: IO 0x0018001000..0x0018010fff -> 0x0018001000 [ 2.376115] j721e-pcie 2910000.pcie: MEM 0x0018011000..0x001fffffff -> 0x0018011000 [ 2.384395] j721e-pcie 2910000.pcie: IB MEM 0x0000000000..0xffffffffffff -> 0x0000000000 [ 3.393042] j721e-pcie 2910000.pcie: PCI host bridge to bus 0001:00 [ 3.472254] pcieport 0001:00:00.0: PME: Signaling with IRQ 71 [ 3.478616] j721e-pcie 2920000.pcie: host bridge /bus@100000/pcie@2920000 ranges: [ 3.486293] j721e-pcie 2920000.pcie: IO 0x4400001000..0x4400010fff -> 0x0000001000 [ 3.494569] j721e-pcie 2920000.pcie: MEM 0x4400011000..0x4407ffffff -> 0x0000011000 [ 3.502845] j721e-pcie 2920000.pcie: IB MEM 0x0000000000..0xffffffffffff -> 0x0000000000 [ 3.625944] j721e-pcie 2920000.pcie: Failed to init phy [ 3.631311] j721e-pcie: probe of 2920000.pcie failed with error -110

The sdk used is 08_06_00_11.

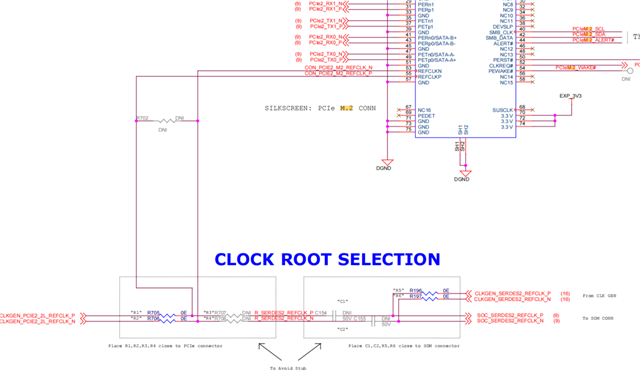

on PCIe_M.2 we modify CON_PCIE2_M2_REFCLK_N/ CON_PCIE2_M2_REFCLK_N from CLKGEN_SERDES2_REFCLK_P/CLKGEN_SERDES2_REFCLK_N to SOC_SERDES2_REFCLK_P/ SOC_SERDES2_REFCLK_N.

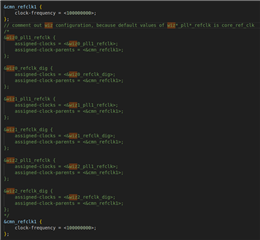

so we want to know how to modify dts/sdti to adapt this?

Regards,

zhang