- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Shine,

I see that TDA4VH is the SoC in use. Could you try below patch for using internal refclk?

enable_internal_ref_clock_out_pcie1_j784s4.patch

Regards,

Takuma

Hi Takuma,

Thank you very much.

diff --git a/board-support/linux-kernel/arch/arm64/boot/dts/ti/k3-j784s4-evm.dts b/board-support/linux-kernel/arch/arm64/boot/dts/ti/k3-j784s4-evm.dts

index 492975144..8a3f17450 100644

--- a/board-support/linux-kernel/arch/arm64/boot/dts/ti/k3-j784s4-evm.dts

+++ b/board-support/linux-kernel/arch/arm64/boot/dts/ti/k3-j784s4-evm.dts

@@ -729,7 +729,7 @@ &serdes1 {

status = "okay";

serdes1_pcie_link: phy@0 {

reg = <0>;

- cdns,num-lanes = <2>;

+ cdns,num-lanes = <4>;

#phy-cells = <0>;

cdns,phy-type = <PHY_TYPE_PCIE>;

resets = <&serdes_wiz1 1>, <&serdes_wiz1 2>;

@@ -745,11 +745,14 @@ &pcie0_rc {

reset-gpios = <&exp1 6 GPIO_ACTIVE_HIGH>;

phys = <&serdes1_pcie_link>;

phy-names = "pcie-phy";

+ status = "okay";

+

};

&pcie0_ep {

phys = <&serdes1_pcie_link>;

phy-names = "pcie-phy";

+ status = "disabled";

};

&pcie1_rc {

@@ -783,7 +786,8 @@ &serdes_ln_ctrl {

<J784S4_SERDES0_LANE2_IP3_UNUSED>, <J784S4_SERDES0_LANE3_USB>,

<J784S4_SERDES1_LANE0_PCIE0_LANE0>, <J784S4_SERDES1_LANE1_PCIE0_LANE1>,

<J784S4_SERDES1_LANE2_PCIE0_LANE2>, <J784S4_SERDES1_LANE3_PCIE0_LANE3>,

- <J784S4_SERDES2_LANE2_QSGMII_LANE1>, <J784S4_SERDES2_LANE3_QSGMII_LANE2>;

+ <J784S4_SERDES2_LANE2_QSGMII_LANE1>, <J784S4_SERDES2_LANE3_QSGMII_LANE2>,

+ <J784S4_SERDES2_LANE2_IP3_UNUSED>,<J784S4_SERDES2_LANE2_IP4_UNUSED>;

};

&main_udmass_inta {

diff --git a/board-support/linux-kernel/drivers/phy/cadence/phy-cadence-torrent.c b/board-support/linux-kernel/drivers/phy/cadence/phy-cadence-torrent.c

index f04619634..34b44c31f 100644

--- a/board-support/linux-kernel/drivers/phy/cadence/phy-cadence-torrent.c

+++ b/board-support/linux-kernel/drivers/phy/cadence/phy-cadence-torrent.c

@@ -2780,6 +2780,27 @@ static int cdns_torrent_phy_probe(struct platform_device *pdev)

if (ret)

goto put_lnk_rst;

}

+ /* Un-lock Partition 7 : 8000h to 9FFFh */

+ writel(0x68EF3490, ioremap(0x011D008, 0x4)); /* LOCK7_KICK0 */

+ writel(0xD172BC5A, ioremap(0x011D00C, 0x4)); /* LOCK7_KICK1 */

+ /* Un-lock Partition 1 : 4000h to 5FFFh */

+ writel(0x68EF3490, ioremap(0x00105008, 0x4)); /* LOCK1_KICK0 */

+ writel(0xD172BC5A, ioremap(0x0010500C, 0x4)); /* LOCK1_KICK1 */

+

+ /* Un-lock Partition 2 : 8000h to 9FFFh */

+ writel(0x68EF3490, ioremap(0x00109008, 0x4)); /* LOCK2_KICK0 */

+ writel(0xD172BC5A, ioremap(0x0010900C, 0x4)); /* LOCK2_KICK1 */

+

+

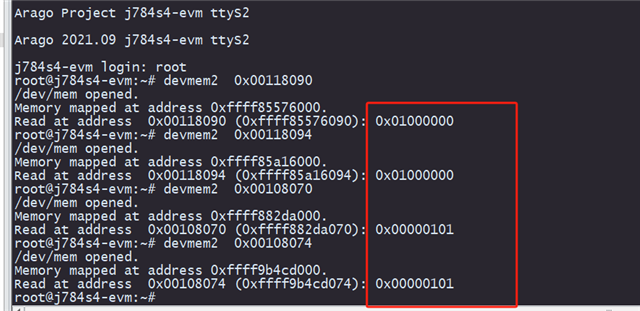

+ /* Enable ACSPCIe0 PAD 0 and 1 */

+ writel(0x01000000, ioremap(0x00118090, 0x4));

+ /* Enable ACSPCIe1 PAD 0 and 1 */

+ writel(0x01000000, ioremap(0x00118094, 0x4));

+

+ /* PCIE_REFCLK0_CLKSEL : EN + MAIN_PLL2_HSDIV4_CLKOUT */

+ writel(0x00000101, ioremap(0x00108070, 0x4));

+ /* PCIE_REFCLK1_CLKSEL : EN + MAIN_PLL2_HSDIV4_CLKOUT */

+ writel(0x00000101, ioremap(0x00108074, 0x4));

phy_provider = devm_of_phy_provider_register(dev, of_phy_simple_xlate);

if (IS_ERR(phy_provider)) {

Test the R860 R859, the voltage changed from 0 to 1.8v, the frequency is changing, not near 100MHz

Note: using VH EVM board

Thanks

Regards

Shine

Hi Shine,

To clarify, are the R860 R859 installed? And is the behavior being seen that voltage is toggling, but not at 100MHz?

I would need a couple of days to look deeper into this.

Regards,

Takuma

Hi Takuma,

To clarify, are the R860 R859 installed?

R860 R859 are not installed.

And is the behavior being seen that voltage is toggling, but not at 100MHz?

The frequency is not correct. It seems that the wave is the noise wave.

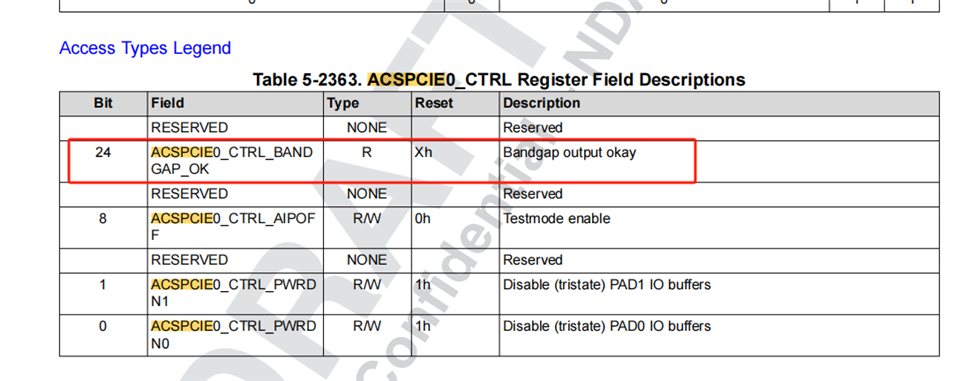

The amplitude variation is due to bit24=1, if setting to 1, it is 1.8v, if setting to 0, it is 0v.

/* PCIE_REFCLK0_CLKSEL : EN + MAIN_PLL2_HSDIV4_CLKOUT */

writel(0x00000101, ioremap(0x00108070, 0x4));

/* PCIE_REFCLK1_CLKSEL : EN + MAIN_PLL2_HSDIV4_CLKOUT */

writel(0x00000101, ioremap(0x00108074, 0x4));

Customer found that the path you selected is MAIN_PLL2_HSDIV4_CLKOUT,

Thanks

Regards

Shine

Hi Shine,

What the patch should do is route the internal clock to the refclk for SERDES configured for PCIe. I will need some time to take a look at it. It looks like some registers are correct since the voltage level is changing, but not all are correct since it looks like noise instead of actual clock.

Regards,

Takuma

Hi Takuma,

Thank you very much.

Patch for SDK7.3:

/cfs-file/__key/communityserver-discussions-components-files/791/0001_2D00_route_2D00_clock_2D00_externally.patch

Patch for SDK8.x:

/cfs-file/__key/communityserver-discussions-components-files/791/pcie_2D00_ref_2D00_clock_2D00_out_5F00_sdk8.diff

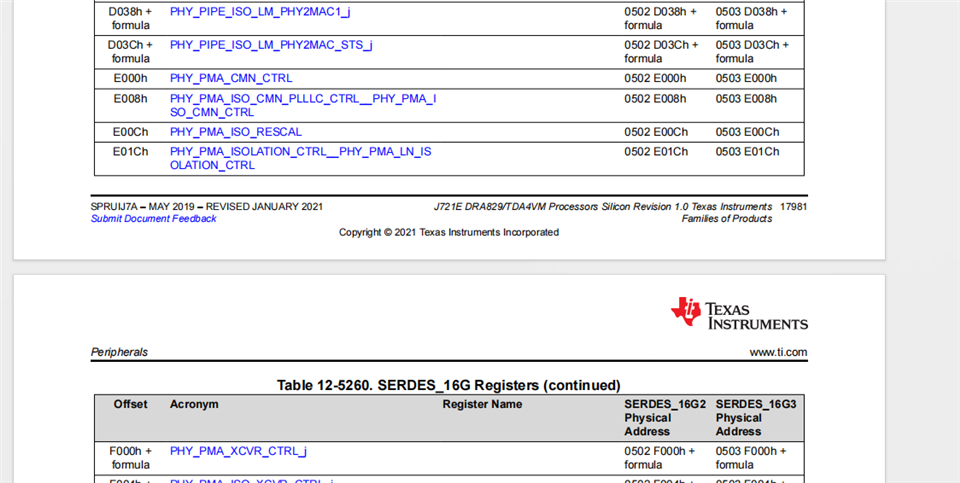

regmap_field_write(cdns_phy->phy_pma_cmn_ctrl_rcv_out_en, 0x3);

regmap_field_write(cdns_phy->cmn_plllc_clk1_en, 0x1);

regmap_field_write(cdns_phy->cmn_plllc_clk1outdiv, 0x2e);

According to the code, the register offset should be e09a, but the register description doesn't mentioned it. Is it not public yet?

Thanks

Regards

Shine

Hi Shine,

Some of the registers might not be in the TRM, because the registers are taken from some IP documentation directly from Cadence.

Although, the patches you are referencing are for the TDA4VM which has a different SERDES called the sierra, whereas TDA4VH has the torrent SERDES, so SERDES register offsets would be different between the two. To clarify, is the device being used the TDA4VH or the TDA4VM?

Regards,

Takuma

Hi Takuma,

Thank you very much.

Customer did the tests on TDA4VH. He referenced the TDA4VM TRM register description which is detailed than VH TRM.

How to configure the serdes to get 100MHz? (The above mentioned pll2 hisdiv 4 is 100M)

Thanks

Regards

Shine

Hi Shine,

Apologies for the delays. Currently looking into this.

Regards,

Takuma

Hi Shine,

I am revisiting some old threads that are open. Is this thread still open?

If yes, I had created a FAQ that deals with the second PCIe port not outputting a 100MHz refclk: https://e2e.ti.com/support/processors-group/processors/f/processors-forum/1230896/faq-j784s4xevm-how-to-enable-second-pcie-slot-for-two-ssd-cards

As mentioned in the FAQ, in 9.0 SDK and onward, there is a patch that enables the internal refclk for the second PCIe port to provide the 100MHz refclk to the PCIe port, so a hardware change is not necessary.

However, if you would like to switch PCIe0 instance to use internal clock, software changes and hardware changes would be necessary, since the port is physically connected to the external reference clock instead of the internal clock.

Regards,

Takuma