Part Number: TDA4VM

Hi Experts

my customer meet SGMII port ping failure issue, I need your help

【Problem phenomenon】

The SGMII port on the board can be brought up, but cannot ping.

There are already other RGMII ports, that can be pinged successfully.

【Schematic】

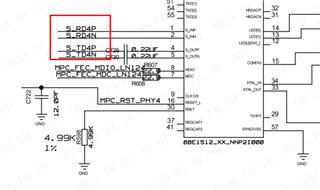

This interface uses CPSW PORT5 and connects to phy (Marvel 88e1512) through lan0 of Serdes4. See the diff below for specific modifications

【DTS】

DTS modification, in addition to the current SGMII port (CPSW9G_PORT5) modification, there is also an RGMII port in the MCU domain, and two RGMII ports (CPSW9G_PORT3, PORT8) in the main domain. The RGMII port can be pinged.

The configuration of the SGMII port is modified with reference to the e2e patch: TDA4VM: SGMII device tree overlays - Processors forum - Processors - TI E2E support forums

【log】

See attachment

【Version】

SDK 8.6.1

kernel 5.10.162

【Register】

【Problem found】

The pll has been locked, but the auto-negotiation failed, and the link is not up.

CPSW_SGMII_STATUS_REG_ 0x0C000514 0x00000030

https://e2e.ti.com/cfs-file/__key/communityserver-discussions-components-files/791/k3_2D00_j721e_2D00_sk.dts.patch

https://e2e.ti.com/cfs-file/__key/communityserver-discussions-components-files/791/k3_2D00_j721e_2D00_mcu_2D00_wakeup.dtsi.patch

https://e2e.ti.com/cfs-file/__key/communityserver-discussions-components-files/791/k3_2D00_j721e_2D00_main.dtsi.patch