Hi,

My customer has a question about how to set the frequency of OSPI_CLK on the Device Tree.

How should they write or add to the Device Tree dts file to set OSPI_CLK to 105.3MHz?

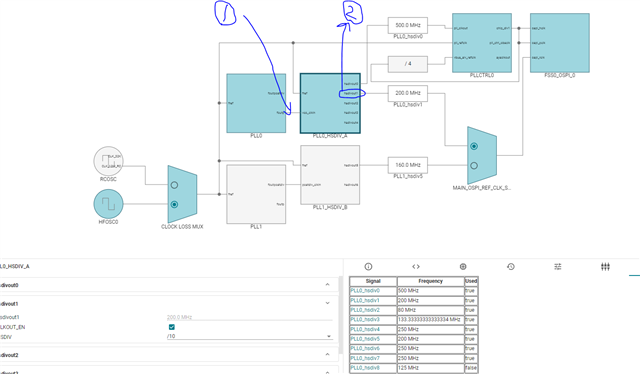

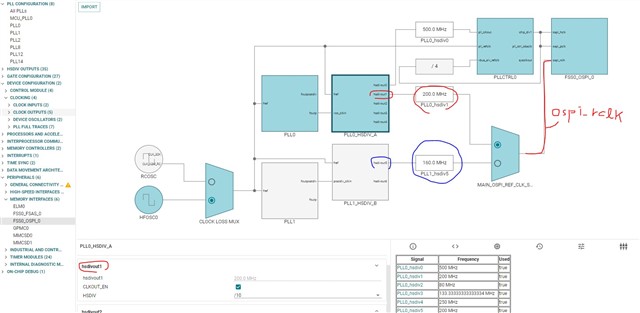

At the Device Tree in the SDK, they changed the value of spi-max-frequency = <25000000>; and set the frequency of OSPI_CLK to 105.3MHz (2GHz divided by 19), but it was not controlled at all when they checked the register value of the corresponding PLL (described below). Also, when they checked the waveform on the actual device, the OSPI_CLK output was only around 80MHz.

They also checked the register value of the baud rate after that (this means the baud rate immediately before the OSPI_CLK output after the PLL), and there were no unexpected baud rate values or unexpected frequency.

The corresponding PLL Register

Address 0x00680084 PLL0_HSDIV_CTRL1 (Bit 6-0)

From dts file Device Tree

&ospi0 {

pinctrl-names = "default";

pinctrl-0 = <&ospi0_pins_default>;

reg = <0x00 0x0fc40000 0x00 0x100>,

<0x00 0x60000000 0x00 0x04000000>,

<0x00 0x64000000 0x00 0x01000000>;

cs-gpios = <0>, <0>; /* 2 Native CS0,1 */

flash@0{

compatible = "jedec,spi-nor";

reg = <0x0>;

spi-tx-bus-width = <8>;

spi-rx-bus-width = <8>;

spi-max-frequency = <25000000>; <== Tried to change this frequency to 105.3MHz, but the actual waveform and corresponding register will not be as set.

cdns,tshsl-ns = <60>;

cdns,tsd2d-ns = <60>;

cdns,tchsh-ns = <60>;

cdns,tslch-ns = <60>;

cdns,read-delay = <4>;

cdns,phy-mode;

#address-cells = <1>;

#size-cells = <1>;

};

fram@1{

compatible = "jedec,spi-nor";

reg = <0x1>;

spi-tx-bus-width = <4>;

spi-rx-bus-width = <4>;

spi-max-frequency = <25000000>;

cdns,tshsl-ns = <60>;

cdns,tsd2d-ns = <60>;

cdns,tchsh-ns = <60>;

cdns,tslch-ns = <60>;

cdns,read-delay = <4>;

cdns,phy-mode;

#address-cells = <1>;

#size-cells = <1>;

};

Clock Tree

Regards,

Hideaki