- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Dear TI experts

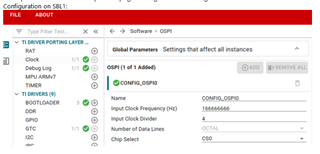

I want to set the OSPI0 clock to 160MHz

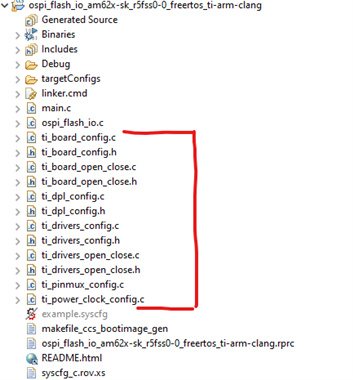

I'm trying to change the clock config here:

Besides, We found the OSPI clocking settings in this area:

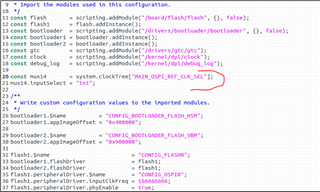

But when we add 2 line of code below to the *.syscfg file,

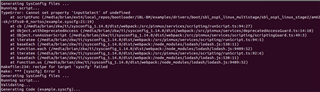

we face the build error like this:

Can you tell me how to switch the MAIN_OSPI_REF_CLK_SEL into

160.0MHz

Thanks,

Cong.

Hi,

Thanks for the query. I have taken your inputs and will revert back soon.

Regards,

Tushar

Hi Cong,

You are trying to set frequency of OSPI0 to 160.0 MHz, you can simply set it in the SysConfig file.

Once you build, the files generated will surely have the configuration of 160 MHz set for OPSI0.

Regards,

Vaibhav

Hi Cong,

I understood, what you are trying to do.

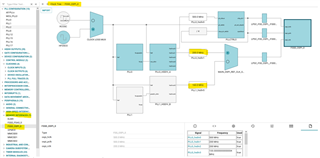

So from Clock Tree Tool, you set 160.0 MHz for MAIN_OSPI_REF_CLK_SEL and got a file generated.

Currently, we are not supporting addition of generated configurations from clock tree tool straight into .sysconfig file.

Regards,

Vaibhav

Hi Cong,

As mentioned earlier we are not supporting the addition of generated configurations from clock tree tool to example.sysconfig file as of now.

So, I have got a work around for you by the help of which you can set the OSPI clock frequency to 160 MHz.

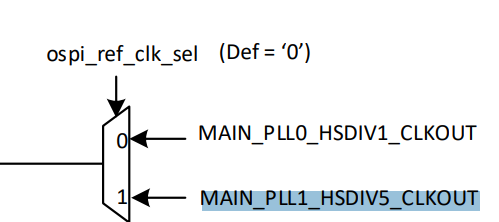

Please look at the diagram below:

The two clocks are:

Based on your usecase, we will use the second one which provides 160 MHz.

Follow the steps below:

SOC_ModuleClockFrequency gSocModulesClockFrequency[] = {

{ TISCI_DEV_FSS0_OSPI_0, TISCI_DEV_FSS0_OSPI_0_OSPI_RCLK_CLK_PARENT_POSTDIV1_16FFT_MAIN_1_HSDIVOUT5_CLK, 160000000 },

{ TISCI_DEV_WKUP_UART0, TISCI_DEV_WKUP_UART0_FCLK_CLK, 48000000 },

{ SOC_MODULES_END, SOC_MODULES_END, SOC_MODULES_END },

};

Now you should be good to go.

Regards,

Vaibhav

Hello Vaibhav,

Thanks for your reply

Currentlly, we can set the clock of SBl1 to 160 Mhz correctlly, but we face an issue on linux side: the output of OSPI clock is not correct.

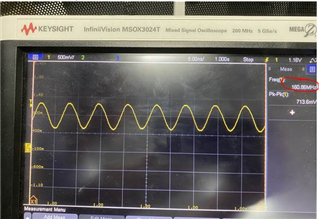

The OSPI output clock is captured on the actual ZKW ECU from SBL1 stage is 160.66MHz

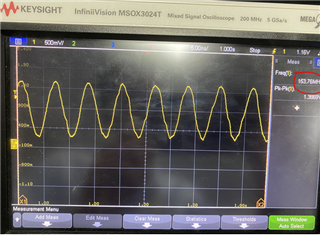

Continue to modify on Linux side: Output of OSPI is 153.67MHz

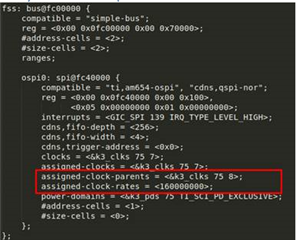

dts:

waweform:

Could you please tell me

1.Why is there consistence of OSPI clock between SBL stage and Linux stage?

2.How can we set the clock of OSPI on linux exactly to 160Mhz?

Closing out this thread by adding back into from an offline discucssion.

1.Why is there consistence of OSPI clock between SBL stage and Linux stage?

The clock was initialized with different frequencies, at SBL vs. Linux stage.

2.How can we set the clock of OSPI on linux exactly to 160Mhz?

We need modify the assigned-clock-parents property of the ospi0 node to select the same input (“parent”) as it was suggested earlier. In the device tree file you can do this like this (note this is on the SK-AM62 board with stock SDK v8.6):

$ git diff

diff --git a/arch/arm64/boot/dts/ti/k3-am62-main.dtsi b/arch/arm64/boot/dts/ti/k3-am62-main.dtsi

index 510775e9a88f..8100879cdaa1 100644

--- a/arch/arm64/boot/dts/ti/k3-am62-main.dtsi

+++ b/arch/arm64/boot/dts/ti/k3-am62-main.dtsi

@@ -628,8 +628,8 @@ ospi0: spi@fc40000 {

cdns,trigger-address = <0x0>;

clocks = <&k3_clks 75 7>;

assigned-clocks = <&k3_clks 75 7>;

- assigned-clock-parents = <&k3_clks 75 8>;

- assigned-clock-rates = <166666666>;

+ assigned-clock-parents = <&k3_clks 75 9>; /* Select PARENT_POSTDIV1_16FFT_MAIN_1_HSDIVOUT5_CLK */

+ assigned-clock-rates = <160000000>;

power-domains = <&k3_pds 75 TI_SCI_PD_EXCLUSIVE>;

#address-cells = <1>;

#size-cells = <0>;If I do this I can see how the input clock to the OSPI module changes in Linux, as follows.

Before (see how clock parent 8 feeds the RCLK with clock ID 7 with 166.66MHz)

root@am62xx-evm:/# k3conf dump clock 75 |--------------------------------------------------------------------------------| | VERSION INFO | |--------------------------------------------------------------------------------| | K3CONF | (version v0.1-88-g982f5c2 built Fri Feb 24 05:07:09 UTC 2023) | | SoC | AM62X SR1.0 | | SYSFW | ABI: 3.1 (firmware version 0x0008 '8.6.4--v08.06.04 (Chill Capybar)') | |--------------------------------------------------------------------------------| |-------------------------------------------------------------------------------------------------------------------------------------| | Device ID | Clock ID | Clock Name | Status | Clock Frequency | |-------------------------------------------------------------------------------------------------------------------------------------| | 75 | 0 | DEV_FSS0_OSPI_0_OSPI_DQS_CLK | CLK_STATE_READY | 0 | | 75 | 1 | DEV_FSS0_OSPI_0_OSPI_HCLK_CLK | CLK_STATE_READY | 500000000 | | 75 | 2 | DEV_FSS0_OSPI_0_OSPI_ICLK_CLK | CLK_STATE_READY | 0 | | 75 | 3 | DEV_FSS0_OSPI_0_OSPI_ICLK_CLK_PARENT_BOARD_0_OSPI0_DQS_OUT | CLK_STATE_READY | 0 | | 75 | 4 | DEV_FSS0_OSPI_0_OSPI_ICLK_CLK_PARENT_BOARD_0_OSPI0_LBCLKO_OUT | CLK_STATE_READY | 0 | | 75 | 5 | DEV_FSS0_OSPI_0_OSPI_OCLK_CLK | CLK_STATE_READY | 0 | | 75 | 6 | DEV_FSS0_OSPI_0_OSPI_PCLK_CLK | CLK_STATE_READY | 500000000 | | 75 | 7 | DEV_FSS0_OSPI_0_OSPI_RCLK_CLK | CLK_STATE_READY | 166666666 |<--+ | 75 | 8 | DEV_FSS0_OSPI_0_OSPI_RCLK_CLK_PARENT_HSDIV4_16FFT_MAIN_0_HSDIVOUT1_CLK | CLK_STATE_READY | 166666666 |---+ | 75 | 9 | DEV_FSS0_OSPI_0_OSPI_RCLK_CLK_PARENT_POSTDIV1_16FFT_MAIN_1_HSDIVOUT5_CLK | CLK_STATE_READY | 160000000 | |-------------------------------------------------------------------------------------------------------------------------------------|

After (see how now clock parent 9 feeds the RCLK with clock ID 7 with 160MHz)

root@am62xx-evm:~# k3conf dump clock 75 |--------------------------------------------------------------------------------| | VERSION INFO | |--------------------------------------------------------------------------------| | K3CONF | (version v0.1-88-g982f5c2 built Fri Feb 24 05:07:09 UTC 2023) | | SoC | AM62X SR1.0 | | SYSFW | ABI: 3.1 (firmware version 0x0008 '8.6.4--v08.06.04 (Chill Capybar)') | |--------------------------------------------------------------------------------| |-------------------------------------------------------------------------------------------------------------------------------------| | Device ID | Clock ID | Clock Name | Status | Clock Frequency | |-------------------------------------------------------------------------------------------------------------------------------------| | 75 | 0 | DEV_FSS0_OSPI_0_OSPI_DQS_CLK | CLK_STATE_READY | 0 | | 75 | 1 | DEV_FSS0_OSPI_0_OSPI_HCLK_CLK | CLK_STATE_READY | 500000000 | | 75 | 2 | DEV_FSS0_OSPI_0_OSPI_ICLK_CLK | CLK_STATE_READY | 0 | | 75 | 3 | DEV_FSS0_OSPI_0_OSPI_ICLK_CLK_PARENT_BOARD_0_OSPI0_DQS_OUT | CLK_STATE_READY | 0 | | 75 | 4 | DEV_FSS0_OSPI_0_OSPI_ICLK_CLK_PARENT_BOARD_0_OSPI0_LBCLKO_OUT | CLK_STATE_READY | 0 | | 75 | 5 | DEV_FSS0_OSPI_0_OSPI_OCLK_CLK | CLK_STATE_READY | 0 | | 75 | 6 | DEV_FSS0_OSPI_0_OSPI_PCLK_CLK | CLK_STATE_READY | 500000000 | | 75 | 7 | DEV_FSS0_OSPI_0_OSPI_RCLK_CLK | CLK_STATE_READY | 160000000 |<--+ | 75 | 8 | DEV_FSS0_OSPI_0_OSPI_RCLK_CLK_PARENT_HSDIV4_16FFT_MAIN_0_HSDIVOUT1_CLK | CLK_STATE_READY | 200000000 | | | 75 | 9 | DEV_FSS0_OSPI_0_OSPI_RCLK_CLK_PARENT_POSTDIV1_16FFT_MAIN_1_HSDIVOUT5_CLK | CLK_STATE_READY | 160000000 |---+ |-------------------------------------------------------------------------------------------------------------------------------------

Regards, Andreas