Hi,expert

I found only 20MHz when measuring the clock of opsi0, but I set the spi max frequency value to 25M in the device tree. I printed the value of cqspi ->sclk in the spi cadence quadspi. c file, which is also 25M.What is the reason for the inconsistency between the setting and the measurement results.

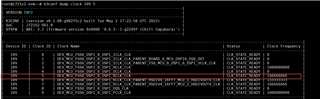

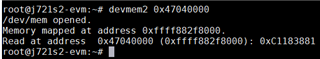

Another question is that I know that the refclk cycle of OSPI is Device ID 109 Clock ID 5, also known as DEV_ MCU_ FSS0_ OSPI_ 0_ OSPI_ RCLK_ CLK, with a value of 166666666 and a division coefficient of 3, can be read from register 0x47040000 bit [22:19], so the final clock should be 166666666/3=55.5MHz?

DEV_MCU_FSS0_OSPI_0_OSPI_RCLK_CLK:

div vlaue:

Best Regards,

Bing