Hi,

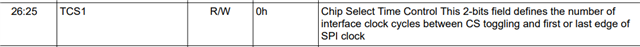

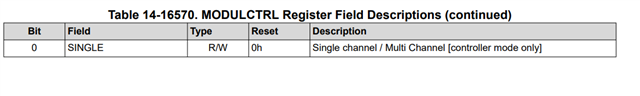

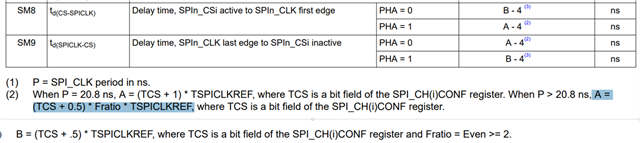

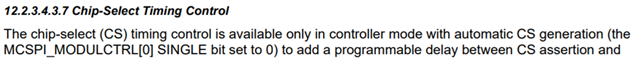

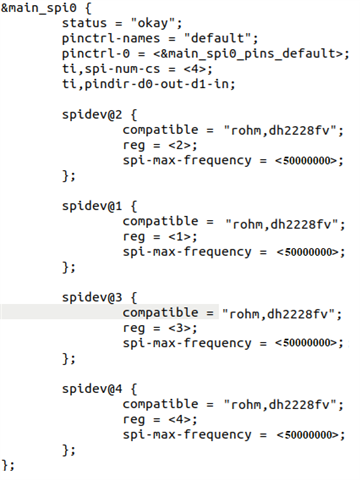

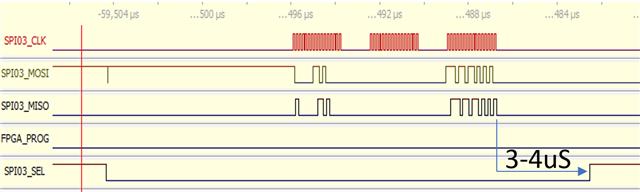

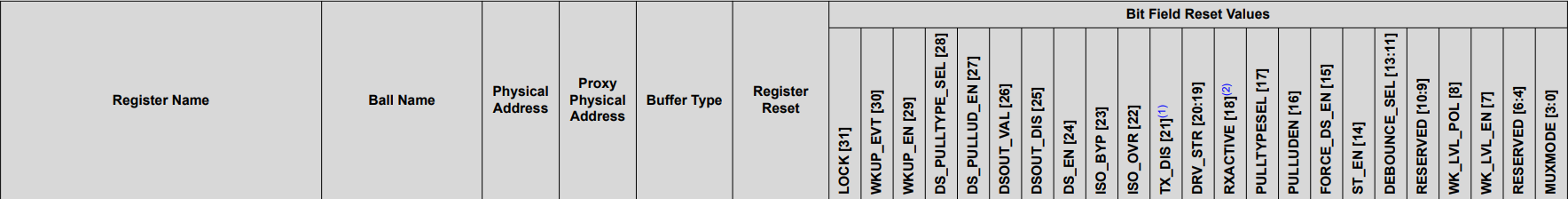

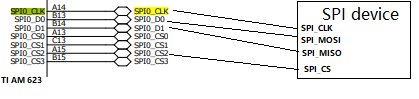

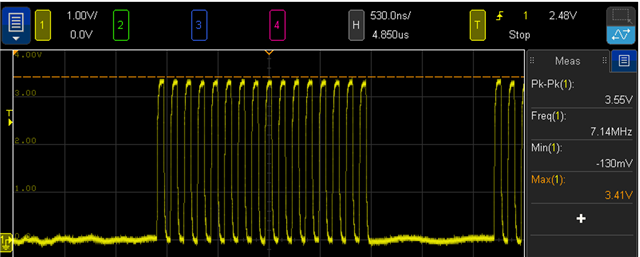

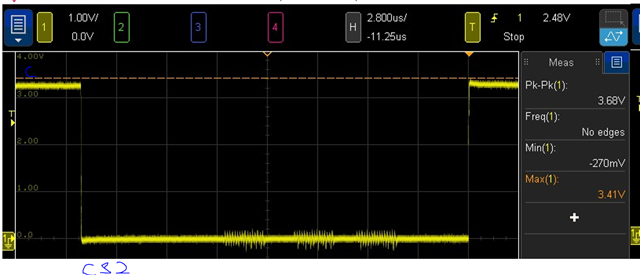

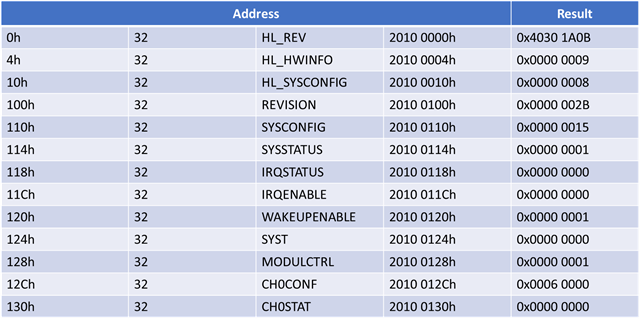

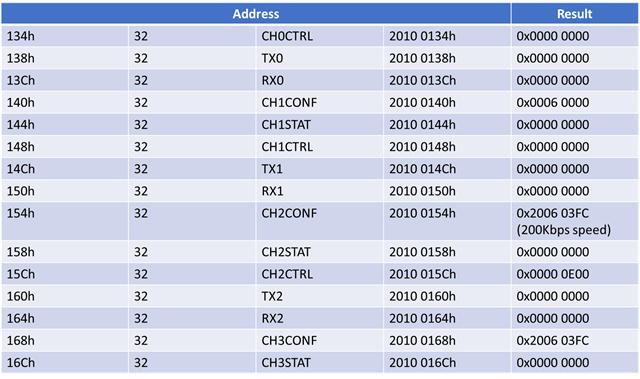

I'm using TI AM623, I configured SPI0 to use ~7Mhz and I noticed that the SPI Chip select 2 required 4us to deactivate after last spi clock. According to data sheet, it can be configured to only need 0.5 clock cycle which is in hundred nano seconds, I checked the register of the TCS1, it's 0 (is this means no extra delay, which is about 0.5 cycle?). Is this TCS1 only applicable for single channel where MODULCTRL bit 0 = 0? How can I make it to only have less than 1uS?