- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi TI Experts,

I have the below queries regarding Power supply sequencing between SOC (Processor) and the Attached devices

This FAQ applies to AM335x, AM64x, AM437x, AM62x, AM62Ax, AM62Px

Hi Board designers,

Refer below inputs for the Power sequencing between SOC (Processor) and the Attached devices related queries.

Definitions

What is a fail-safe IO pin?

* A fail-safe IO pin is designed so that external voltage can be connected to the IO terminal, even when the IO pin's power supply is turned off.

* An IO pins that is NOT fail-safe should never have external voltage applied to the pin when the IO pin's power supply is turned off.

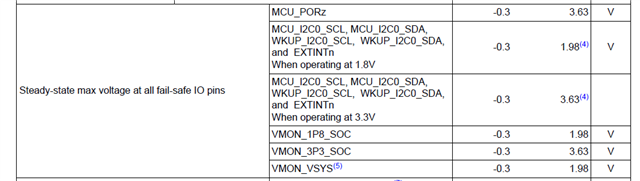

* For more information about the valid input voltage range for both fail-safe and non-fail-safe pins, refer to the "Absolute Maximum Ratings" section of the processor's device tree.

Most of the processor IOs are not fail-safe. Any time a peripheral device is powered from a different power source than the SOC, the peripheral must NEVER apply power to the IO pin that is outside of the valid input voltage range. The Power supply is required to be ramped and stable before the SOC (Processor) IOs are driven by external inputs.

Refer the data-sheet for information on available fail-safe IOs.

It is recommended to power the IOs of the external device from the same power source as the respective SOC (Processor) IOs to ensure the external device never applies potential to an SoC IO that is not powered. This is needed to protect the IOs of both devices.

The core supply for the attached devices can be applied from an independent power source.

There are 2 possible options - the board designer needs to route the IO power rails from the SOM generated power supplies to the base board to power attached devices, or place the PMIC on the base board and route all of the supplies to the SOM.

The interface signals between the SOC (Processor) and the attached device that could be driven to a voltage level outside of the recommended operating voltage, needs to be isolated using FET switches or FET BUS switches.

FET bus switches have been used in the Starter Kit design for other applications but these devices could be used for signal isolation. The FET bus switches are recommended to be enabled by an ANDing logic. The Power good output from the power sources of the SOC (Processor) and the attached device are the inputs to the FET bus switch.

Refer below summary of fail-safe IOs for AM625

Refer to the below section of the data sheet

Specifications

Absolute Maximum Ratings

Regards,

Sreenivasa

Additional notes from the AM625 / AM623 / AM625SIP / AM625-Q1 / AM620-Q1 / AM62A7 / AM62A3 Schematic Design and Review Checklist

Signal Isolation for Fail-Safe Operation

In case the processor and the attached devices or an additional host are powered by different power sources, signal isolation is recommended since most of the processor IOs are not fail-safe. It is recommended to route the signals through a FET bus switch circuit designed to automatically isolate the two devices anytime the IO power is not valid for both devices. The FET bus switch and control logic are recommended to be powered from an always on power supply and only enabled by an AND function of power good signals from different power sources.

Attached device

An attached device includes any device that is interfaced to the SoC (Similar SoC, Different SoC, MCU, Memory, Interface devices or any external devices that sends or receives data).