Hi experts.

we have a problem on the NAND FLASH.

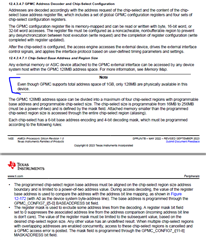

we found the GPMC (AM62X datasheet):

Supports up to 4 independent chip-select regions of programmable size and programmable base addresses on 16MB, 32MB, 64MB, or 128MB boundary in a total address space of 1GB.

but now we use a nand with 2048MBytes 。the system can work .

why the system can work on the space of 2GB ,but the interface just has a total address space of 1GB ?