Part Number: TDA4VM

Hi,

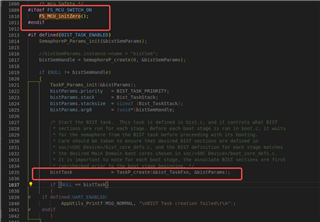

We use SDK 8.6 and run it in MCU 1_ Many security features have been enabled on 0, and it has been found that there is a probability of only printing the first two logs on the Linux side during startup. Have you encountered this problem before? Where should we look for the problem?

Regards,

Guocai Yang