Hi Team,

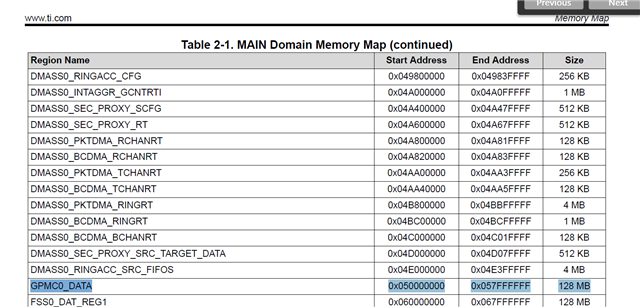

Why GPMC0_DATA Memory map is different?

Best Regards,

Zane

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello Zane,

Please confirm the TRM revision you are using.

Please check the latest TRM on TI.com.

Regards,

Sreenivasa

Hello Zane,

0x50000000 is the correct address for GPMC0_DATA

We have an FAQ that provides links to key collaterals including the TRM

Regards,

Sreenivasa

Hi Sreenivasa,

Can you help me confirm if the following understanding is correct?

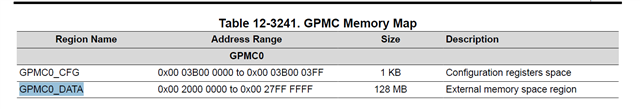

GPMC IP actually supports 1GB memory mapping (AM65 SOC memory mapping 1GB address space), but the memory mapping of GPMC on AM62 only allocates 128MB. If 4 chip selects are used, each chip select has a 32MB memory map to store data.

But what is the maximum external memory capacity that each chip select can support?

Best Regards,

Zane

Hello Zane,

Thank you.

GPMC IP actually supports 1GB memory mapping (AM65 SOC memory mapping 1GB address space), but the memory mapping of GPMC on AM62 only allocates 128MB. If 4 chip selects are used, each chip select has a 32MB memory map to store data.

But what is the maximum external memory capacity that each chip select can support?

Your understanding is correct.

I do not believe there is a max size per CS specified (from hardware side)

If you are operating in synchronous mode we do not recommend using multiple CS chip select due to the challenges related to signal integrity and the effect on the performance.

Regards,

Sreenivasa

Since there is no activity for more than 6 months, will close the ticket. Please submit a new ticket if there is still issues.

Br, Tommy