Other Parts Discussed in Thread: AM620-Q1, , AM623, , , AM62D-Q1, TPS65219, SK-AM62B-P1, SK-AM62-LP, SK-AM62B, SK-AM62, SYSCONFIG

Hi TI Experts,

Can you provide a List of collaterals that can be referred when starting a custom board hardware design.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi TI Experts,

Can you provide a List of collaterals that can be referred when starting a custom board hardware design.

Hi Board designers,

The below links are a quick reference to the collaterals that can be referred when starting a custom design.

Device Selection and features

Product Page

https://www.ti.com/product/AM625

Note:

Any AM62x device implemented in the ALW package will be pin2pin compliant to all other AM62x devices implemented in the ALW package.

Datasheet

AM62x Sitara Processors datasheet

https://www.ti.com/lit/pdf/sprsp58

Silicon Errata

AM62x Processor Silicon Revision 1.0

https://www.ti.com/lit/pdf/sprz487

Technical Reference Manual

AM62x Sitara Processors Technical Reference Manual

https://www.ti.com/lit/pdf/spruiv7

Technical Reference Manual W/o registers

Custom Board design:

Hardware Design Considerations

Hardware Design Considerations for Custom Board Using AM625, AM623, AM625SIP, AM625-Q1, AM620-Q1 Family of Processors

https://www.ti.com/lit/pdf/sprad05

Schematic Design and Review Checklist

AM62x Processor Family (Recommended)

AM623, AM625, AM625SIP, AM620-Q1, AM625-Q1 Processor Family Schematic Design Guidelines and Schematic Review Checklist

https://www.ti.com/lit/pdf/sprado3

AM62X processor families (For references)

AM62x, AM62Ax, AM62D-Q1 and AM62Px Processor Families Schematic, Design Guidelines and Review Checklist

https://www.ti.com/lit/pdf/sprad21

Power Consumption

AM62x Maximum Current Ratings

Enabling Low Power Embedded Systems With AM62x Processors

www.ti.com/.../sprad41.pdf

AM62x Power Consumption

www.ti.com/.../spradg1.pdf

https://www.ti.com/lit/pdf/sprada6

AM62x Power Estimation Tool

https://www.ti.com/lit/pdf/sprad31

AM62x Power Consumption

https://www.ti.com/lit/pdf/spradg1

SoC power solutions Application notes:

Discrete Power Solution for AM62x

https://www.ti.com/lit/pdf/sluaak2

Powering the AM62x with the TPS65219 PMIC

https://www.ti.com/lit/pdf/slvafd0

Evaluation - EVM

SK-AM62B-P1 Design Package Content Overview (Rev. A)

www.ti.com/.../SK-AM62B-P1

www.ti.com/.../sprt777

Design File Package

www.ti.com/.../spar001

SK-AM62-LP Design Package Content Overview

www.ti.com/.../SK-AM62-LP

www.ti.com/.../sprt778

Design File Package

https://www.ti.com/lit/zip/sprr471

SK-AM62B Design Package Folder and Files List

www.ti.com/.../SK-AM62B

www.ti.com/.../sprt784

Design File Package

www.ti.com/.../sprr481

AM62x starter kit for Sitara processors

www.ti.com/.../SK-AM62

Design File Package

https://www.ti.com/lit/zip/sprr448

SysConfig (Pinmux) for SK-AM62 and SK-AM62-P1

SysConfig (Pinmux) for for SK-AM62B

https://e2e.ti.com/cfs-file/__key/communityserver-discussions-components-files/791/am62x_5F00_sk.syscfg

EVM design files in Altium format

Allegro file

.ALG file

https://e2e.ti.com/cfs-file/__key/communityserver-discussions-components-files/791/Layout_5F00_AM62_5F00_0.5mm_5F00_V124_5F00_converted_5F00_v2.brd.alg

Schematics (Reference) for RMII interface

Note: We did functionally validate the common clock configuration. No other clocking options were tested.

Ethernet PHY daughter card

https://www.ti.com/tool/DP83867-EVM-AM

https://www.ti.com/tool/DP83826-EVM-AM2

https://www.ti.com/tool/TIDA-00928

There seems to be a muxed GPMC interface implemented.

https://media.digikey.com/pdf/Data%20Sheets/Texas%20Instruments%20PDFs/TMDXICE3359_SCH.pdf

CAD symbols

CAD symbol specific to the selected device can be chosen from the device product page. Refer below:

https://www.ti.com/product/AM625#cad-cae-symbols

Ordering & quality

https://www.ti.com/product/AM625#order-quality

Package pad diameter and substrate pad dimension

AM625 -> ALW pkg: ball diameter 0.3mm : substrate pad 0.25mm

The recommendation is 1:1 ratio between PCB pad and substrate pad.

Section and Document reference:

. Width/Spacing Proposal for Escapes

https://www.ti.com/lit/an/sprad13a/sprad13a.pdf

The recommendation is to use 0.25mm (10 mil) BGA landing pads to meet the requirements

Lead finish/Ball material

SnAgCuBi

DDR Board Design and Layout Guidelines

AM62x, AM62Lx DDR Board Design and Layout Guidelines

https://www.ti.com/lit/pdf/sprad06

Escape Routing for PCB Design

AM62 Escape Routing for PCB Design

https://www.ti.com/lit/pdf/sprad13

Design Simulation files

https://www.ti.com/product/AM625#design-tools-simulation

Simulation files provided includes IBIS, IBIS-AMI, BSDL, Thermal model and power-estimation tool (PET)

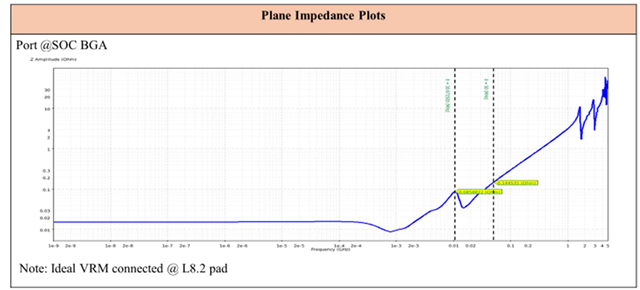

AM62x PDN Target impedance values:

Impedance target values for VDD_CORE on AM625/AM623

Low freq (< 1MHz) : 22mOhm

Mid freq (1 < 20MHz) : 31 mOhm

High freq (20 < 50 MHz) : 40 mOhm

This is valid for either of the core voltages (0.75V, 0.85V) and packages. We do not provide target impedance values for other rails on AM62x.

For frequencies above 50 MHz the board decoupling caps do not play a critical role. SoC and Package decaps (if any) will be dominant beyond 50 MHz

Note:

We do not include Buck output inductance in PDN simulations.

For VDDS_DDR: we do not recommend using target impedance as the signoff for DDR.

Refer to the AM62x, AM62Lx DDR Board Design and Layout Guidelines which outlines all details of power aware SI/PI simulations

that need to be run. The eye mask checks from these power aware simulations are the signoff.

To test PDN analysis SoC and LPDDR4 power line, Customer needs the spec of impedance of SoC/LPDDR4 power line. Could you confirm the impedance?

Here is the plot for the AM62x EVM. However please note that this is an impedance plot of the TI EVM. It should not be used for signoff. The full LPDDR4 system-level simulations must still be run for signoff as prescribed in the LPDDR design guidelines app note.

We only provide impedance targets for VDD_CORE. This information can be found under processor specific section "Example:AM62Ax" (starting on page 31) in the following document: www.ti.com/.../sprac76

As noted in the document, rails not listed are not simulated by TI due to low load transients. For more information, see the device-specific EVM layout for example implementation of these rails.

Other rails like the IOs are highly dependent on external peripherals. From the SoC perspective, if you look at the MAX current ratings for the IOs, the total current (after combining all the IOs of the same voltage) is still very low < 350mA so we don't simulate this rails/No data available.

Regarding your other questions related to PET, the supply names are not expected to match with processor (Example AM62A) pin names because the power estimates in the PET are itemized by supply groups. The power supply consolidation for these supply groups match the EVM.

Power Distribution Networks: Implementation and Analysis

Sitara Processor Power Distribution Networks: Implementation and Analysis

https://www.ti.com/lit/pdf/sprac76

Note: The decoupling capacitor numbers and type on the SK/EVM are only intended to serve as a guideline for customers. The true pass/fail criteria is the target impedance published in the PDN app note.

High Speed Board design and Signal integrity simulation

https://www.ti.com/lit/pdf/spraar7

https://www.ti.com/lit/pdf/spracn9

https://www.ti.com/lit/pdf/sprabi1

SYSCONFIG

DDR subsystem register configuration tool

Technical Documents

Collaterals and application notes

https://www.ti.com/product/AM625#tech-docs

Technical Support

AM625 Custom board design - FAQs

Previous E2E threads - Keywords AM625

Starting a new thread

Useful links

Sitara family of processors FAQ master list

Other FAQs

Notes

Regards,

Sreenivasa

Hi All,

Do we have any information about chemical cleaning processes during the manufacturing? Are there certain chemicals with which we allow our packages to be cleaned or with which they are not allowed to be cleaned?

Refer below

MSDS for the AM62x ALW solder balls

SACQ MSDS_REN_SAC-Q#ACCURUS#605_MSD_20170830.pdf

Materials used in mold compound and substrate

TI_Product_content for AM62X_Customer Format_16 Jun 2022.xlsx

This should allow customers to check for chemical reactivity of the AM62x SOCs with the cleaning solution.

Regards,

Sreenivasa

Hi Board designers,

Configuring Hysteresis

Data sheet

6.3.10 GPIO

6.3.10.1 MAIN Domain

Table 6-22. GPIO0 Signal Descriptions

Table 6-23. GPIO1 Signal Descriptions

(1) This GPIO input signal has a debounce function. For more information on I/O Debounce configuration, see the TRM Device

Configuration chapter.

6.3.10.2 MCU Domain

Table 6-24. MCU_GPIO0 Signal Descriptions

(1) This GPIO input signal has

TRM

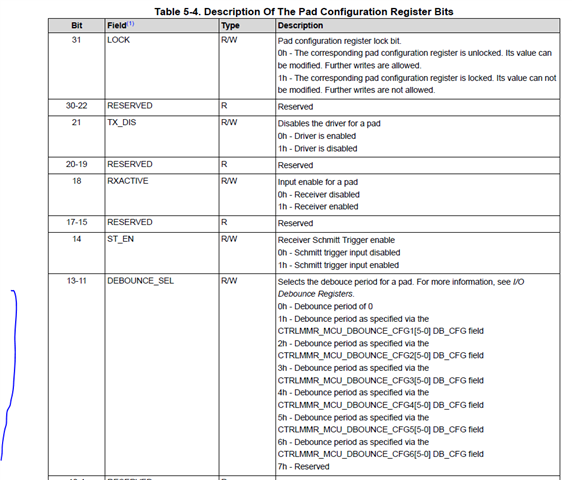

5.1.1.3.1.1 Pad Configuration Registers

The pad configuration registers are used to configure most of the device pads. Each pad configuration register

(PADMMR_PADCONFIG0 to PADMMR_PADCONFIG181) is assotiated only with one pad and has bits as

described in Table 5-4.

14.2.1.2 Pad Configuration Registers

14.2.1.2.1 Pad Configuration Register Functional Description

This is the AM64x description.

Table 14-6172. Description Of The Pad Configuration Register Bits for AM625 will be updated : Bit13-11

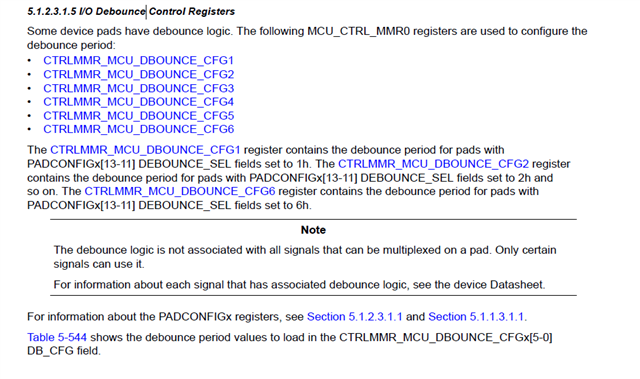

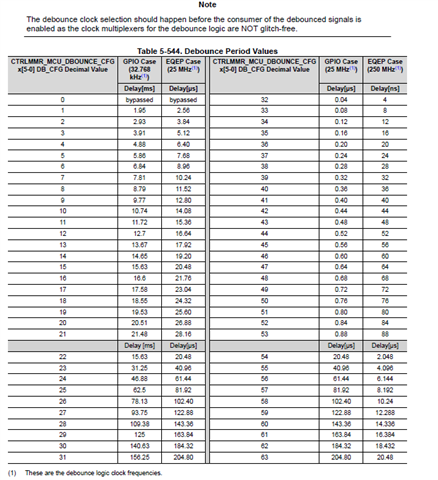

6.1.1.2.1.2 I/O Debounce Control Registers

Table 6-1. Debounce Period Values

This table needs to be updated.

Refer AM64x table

Regards,

Sreenivasa

Hi Board designers,

Refer below information regarding Package's PAD/SMO information needed

e2e.ti.com/.../faq-am625-package-parameter-description

e2e.ti.com/.../faq-am623-package-s-pad-smo-information-needed

Regards,

Sreenivasa

Hi Board designers,

Inputs regarding Package shelf life

Please refer below links

https://www.ti.com/support-quality/quality-policies-procedures/product-shelf-life.html

https://www.ti.com/support-quality/faqs/product-shelf-life-faqs.html

https://www.ti.com/support-quality/reliability/reliability-home.html

https://www.ti.com/lit/an/spraby1a/spraby1a.pdf

https://www.ti.com/lit/pdf/snoa550

https://www.ti.com/lit/an/slva840/slva840.pdf

/cfs-file/__key/communityserver-discussions-components-files/791/Baking-Procedure.pdf

Regards,

Sreenivasa