- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi TI Experts,

Customer is working on AM5728.

Currently they found that when their product (AM5728 inside) initially powered on, the soft-start relay switches on and off once in a moment, the capacitor on Vbus can cause a surge of current, which may have a significant impact on the relay's lifespan.

After some debugging, we have found out the below reasons.

Firstly we have a Control Board and a Power Board, each having a 3V3 supply shown below.

Power_Board_and_Control_Board_Design.pptx

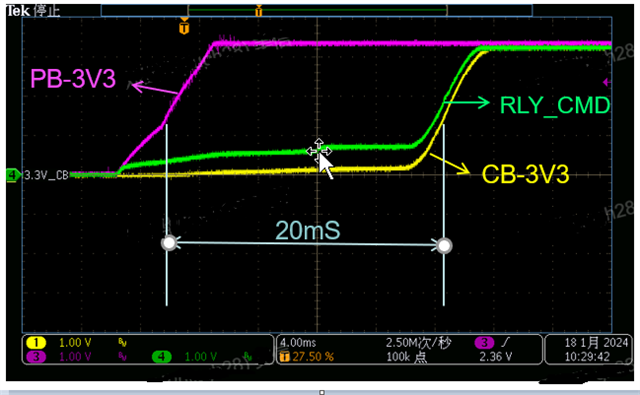

When the power board's 3.3V becomes active, there is a 20ms delay before the control board's 3.3V becomes active.

During this 20ms delay, the pin (AG6, GPIO3.10) of the AM5726 remains at a low level. (Although there is a 1K pull-up resistor to 3.3V, it still remains in low level). We can see from the below diagram for details.

This result seems that AM5726 has a low resistance or it is always at low level when it is not powered on.

May I know the reason here?

Thanks a lot for your support!

Kevin

Hi TI Experts,

My thinking is that, for the AG6, when the SOC is not powered on, it should stay in pull down shown below.

Hence, in customer's situation, there will be revert current goes into the SOC, and due to we have pull down resistor, the voltage of relay should not increase as the PB-3V3 goes up. I think this could explain the reason, could you help to check it pls?

Thanks a lot!

Kevin

The customer system is applying 3.3V to the SOC IO pin before the SOC is energized. This is not a valid operational condition. The SOC must complete a power up sequence before any peripheral components apply a voltage to SOC IOs.

I'd suggest reviewing the entire design to ensure the SOC power seq requirements are met. Perhaps changing the pull up supply or inlcuding a voltage isolation buffer in line will address this concern.