I am referring the collaterals for the below EVM / SK.

SK-AM64B (PROC100A), TMDS64EVM (PROC101C)

Is there any Update to be Done on the collaterals to reuse in my custom design.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Board designers,

Here are some recommended updates based on the learnings for performance improvements.

Schematics - Design Value Updates

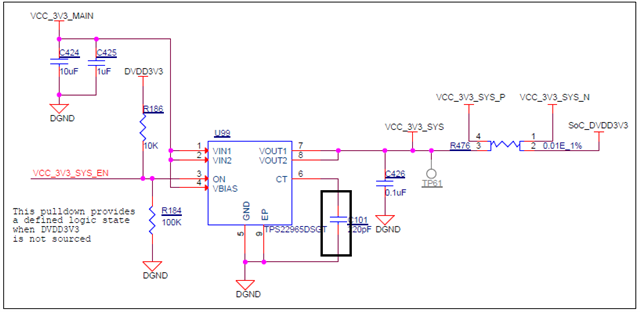

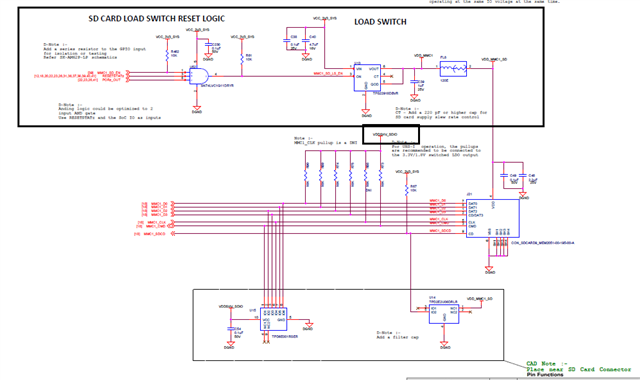

1. VCC_3V3_SYS LOAD SWITCH

SoC IO supply rails have slew rate requirements specified.

Refer Power Supply Slew Rate Requirement section of the data sheet.

Add a cap 220 pF or higher on the Load switch CT (Switch slew rate control) pin.

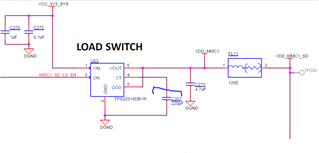

2. SD card power reset Load switch

Add a cap 220 pF or higher on the Load switch CT (Switch slew rate control) pin.

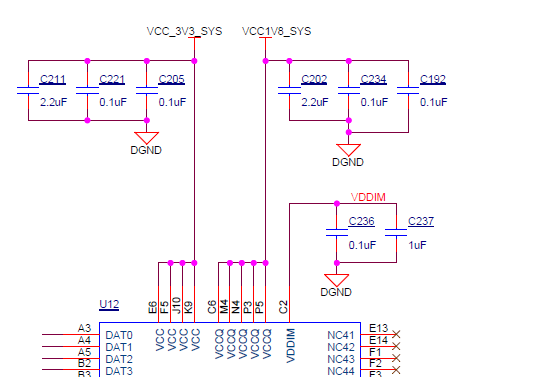

3. eMMC supply decap

Add decaps as required to the eMMC memory supply rails

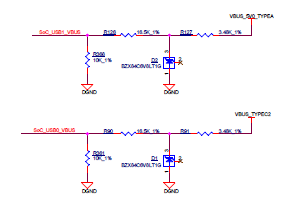

4. USB VBUS divider

5. Provision to Bypass CMC

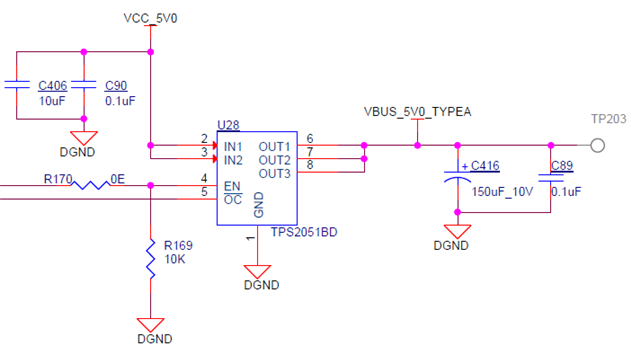

6. USB power switch

Use power switch with OC indication. Connect the OC output of the power switch to SoC input

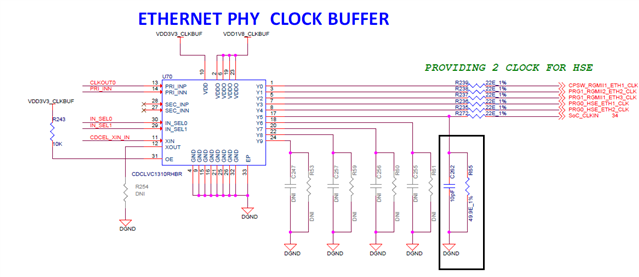

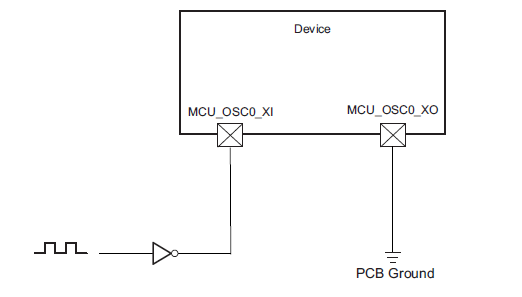

7. SoC clock MCU_OSC0_XI. MCU_OSC0_XO - connecting external clock

DNI the R and C placed at the output of the clock buffer connected to the MCU OSC0 clock input. Placement of these components reduces the amplitude and could affect the performance

8. SoC MCU_OSC0_XO termination - when using external clock

Data sheet section reference : MCU_OSC0 LVCMOS Digital Clock Source

Do not leave XO un connected

The oscillator was designed to measure the differential voltage between XI and XO, for creating a internal reference clock. So there is no guarantee they will get the correct differential input voltage if the XO pin is allowed to float. The datasheet clearly shows this pin needs to be connected to VSS when using an LVCMOS clock source.

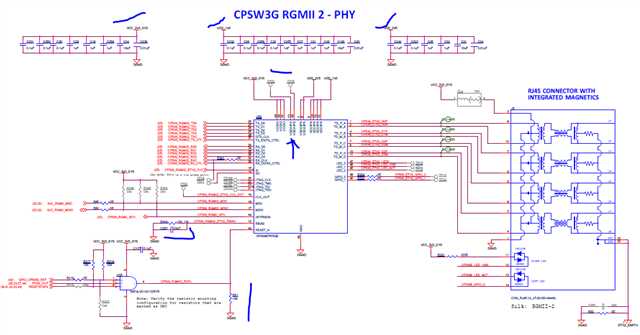

9. Ethernet PHY updates

10. Caution with EPHY 1V and VPP 1.8V LDO

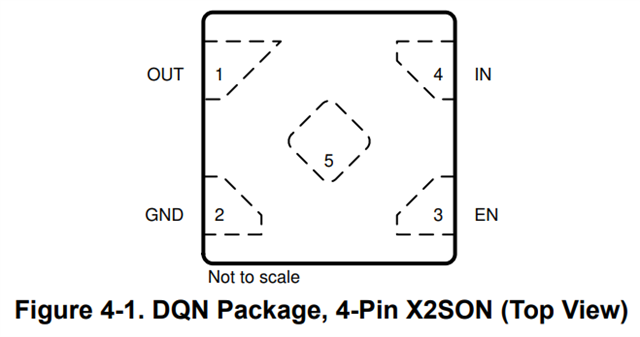

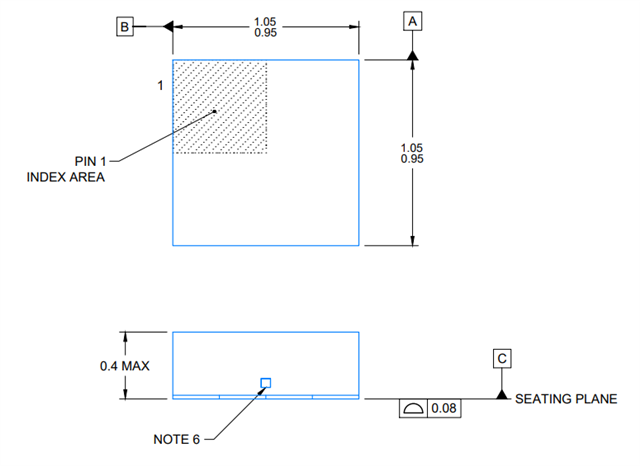

Miniature DQN package used.

Package Outline

PCB pads

There is a likely chance of assembly error due to the LOD outline, pins orientation and the land pattern (pads and pitch)

Take note of the following

EPHY 1.8V supply pins when not used should not be shorted

Note the recommended caps for the EPHY supplies

Note the Rbias R and C values

Note the pulldown for the EPHY Reset

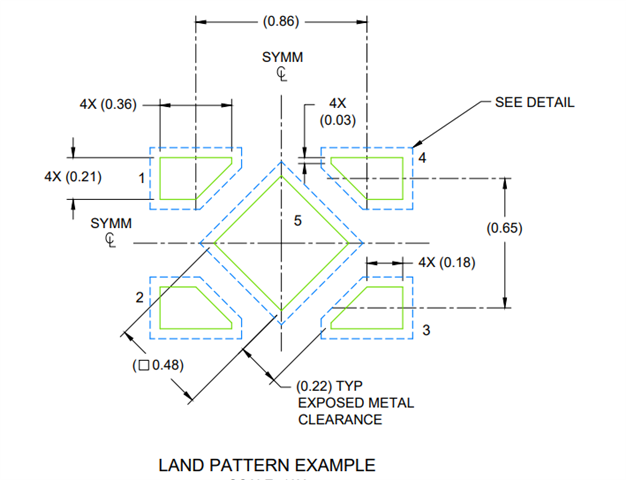

11 EXTINTn RC and pullup

EXTINTn is a open drain output type IO buffer. The IO has slew rate limit requirements when pulled to 3.3V/

Add an RC to limit the slew rate.

Regards,

Sreenivasa

Hi Board designers,

Refer below workarounds when load switch is not used for resetting the SD card power supply and the supply is fixed to 3.3V

Given below are the list of various workarounds that can be done in the device tree node to get SD card working. The workarounds are ordered in increasing order of reducing performance.

All the changes mentioned below, are to be done in the MMCSD device tree node corresponding to the SD instance. This is usually the first (index starting from zero) instance.

· &sdhci1 {· /* SD/MMC */· vmmc-supply = <&vdd_mmc1>;· vqmmc-supply = <&vdd_sd_dv>;· pinctrl-names = "default";· pinctrl-0 = <&main_mmc1_pins_default>;· ti,driver-strength-ohm = <50>;· disable-wp;· sdhci-caps-mask = <0x00000006 0x00000000>; /* Limiting to SDR50 speed mode */· };

· &sdhci1 {· /* SD/MMC */· vmmc-supply = <&vdd_mmc1>;· vqmmc-supply = <&vdd_sd_dv>;· pinctrl-names = "default";· pinctrl-0 = <&main_mmc1_pins_default>;· ti,driver-strength-ohm = <50>;· disable-wp;· no-1-8-v; /* disabling all the UHS modes */};

Regards,

Sreenivasa

Hi Board designers,

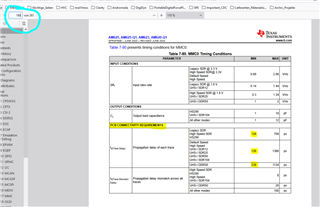

MMC0 PCB Connectivity Requirements

we have issues with an eMMC connected to MMC0 of a AM6254 processor on a custom board.

In the datasheet of the AM625 processors we found layout requirements for the MMC0 interface.

Does this "min" specification mean that the traces of the MMC0 interfaces MUST have a minimum length? If yes can you specify this in inches or mm?

Yes, there is a minimum trace delay requirement for this peripheral.

The delay values are defined with the unit of picoseconds (ps). You will need to determine the propagation velocity of each signal trace on your specific PCB design to know how much additional trace needs to be inserted to achieve the appropriate delay.

Regards,

Sreenivasa

Hi Board designers,

To implement UHS-I refer below steps:

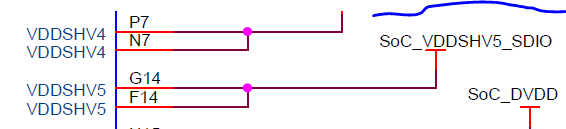

The SD card interface pullups have to be connected to the 3.3V_1.8V VDDSHV_SDIO switched supply output from the PMIC

The SD card needs to be powered using a fixed 3.3V supply.

The 3.3V supply to the SD card needs to be switched through a power switch

Provision to reset the power switch using SOC IOs is recommended

An ANDing logic is recommend to reset the SD cars power switch.

The SOC VDDSHV5 supply needs to be connected to the .3V_1.8V VDDSHV_SDIO switched supply output from the PMIC

e2e.ti.com/.../faq-am6422-sd-host-controller-driver-strength

[FAQ] AM6422: SD Host controller driver strength

Is there an option to select between different driver strength for:

a) 3.3V signaling

b) 1V8 (UHS-I) signaling

The "MMCSD1_CAPABILITIES" Register indicating that Driver Type A,C and D are not supported. However, this register is gets information from "MMCSD1_SS_CTL_CFG_3_REG" Register, where the corresponding bit fields are R/W type. So I can configure that. Does the device supporting driver types A,C and D?

Any other option to adjust driver strength?

No. The drive strength of the SDIO buffer types associated with the MMC1 signals is fixed to 40 ohms.

MMC1 Clock terminations

AM6442: Why only emmc0 can support emmc flash

on AM64x, EMMC0 can connect to emmc flash and emmc1 can only connect to sd/sdio, as emmc don't need SDCD and SDWP, and other pins are same , though the support spec are different:

emmc0: eMMC Electrical Standard 5.1 (JESD84-B51),

sd1: SD Host Controller Standard Specification 4.10 and SD Physical Layer Specification v3.01

customer want to know why emmc1 can not connect to emmc flash, is it only caused by spec difference?

This point will impact their total system design, could you clarify?

Because the design team only closed timing of the MMC0 peripheral for operating with eMMC devices and only closed timing of the MMC1 peripheral for operating with SD Cards.

You need to turn on the receiver associated with the CMD and CLKLB IO cells.

The CMD signal is bidirectional, so the IO cell associated with this pin needs to have its receiver enabled.

The pad associated with the CLKLB IO cell is not bonded to a device pin and it is used to loop a clock through the IO cell and back into the device such that the internal circuits operate from a delayed clock with similar delay that is introduced in the CLK output buffer plus the delay introduced in the DAT input buffers. This is done to help with read timing closure. The internal circuits will not have a clock unless you enable the receiver associated with the unbonded CLKLB IO cell.

There is a note attached to the MMC1 Signal Descriptions table in the datasheet that tells you to keep the default state for the receiver enable associated with PADCONFIG164.

Any pull-ups connected to MMC1 signals must be sourced from the VDDSHV5 power source that changes it operating voltage from 3.3V to 1.8V as the transfer speed increases. They should not be connected to a fixed 3.3V power source.

I just realized the note attached to the MMC1 Signal Descriptions table should say:

For MMC1 to work properly, the RXACTIVE and TX_DIS bits of the CTRLMMR_PADCONFIG164 register must remain in their default state because of retiming purposes.

The original note did not mention the TX_DIS bit requirement.

I would prefer to have CLKLB removed from the SYSCONFIG tool to avoid any chance of someone changing the default state of the RXACTIVE and TX_DIS bits of the CTRLMMR_PADCONFIG164 register, which is the PADCONFIG register associated with the unbounded MMC1_CLKLB IO cell.

Then we would remove the note from the MMC1 Signal Descriptions table because these bits already default to the proper state. The note is only need now because the SYSCONFIG tool is providing a way for customers to accidently change them to an invalid state.

Regards,

Sreenivasa

Hi Board designers,

refer below FAQ for queries related to MCU_OSC0 Start-up Time

Regards,

Sreenivasa

Hi Board designers,

Refer below for description about SPI signal series resistor

In 2.7 System issues of AM64x Schematic Review Checklist.pdf

It says [Put 22-Ω series resistors (close to processor) on the output clocks of the SPI module.], but what are the acceptable tolerances?

Is it possible to use a value such as 33Ω instead of 22Ω?

A value of 33 ohms may actually be better than 22 ohms. The most important thing is placing the resistor close to the AM64x device to minimize the signal trace length that connect the series resistor to the AM64x pin. This is required because the SPI clock pin is operating as input and output at the same time, where the internal data capture clock is looped back in the AM64x IO buffer. This is done to help with timing closure of SPI by inserted an equivalent delay in the looped back clock as the returned data path sees with the delay inserted by the clock output buffer and data input buffer. However, this approach impacts signal integrity at the looped back clock pin.

The help explain this issue, lets assume the output impedance is equal to the trace impedance. In this case the source end of the signal trace will only transition to mid-supply initially when the clock toggles. The signal will propagate the far end of the signal trace where it encounters a high-impedance mismatch which causes an equivalent amplitude reflection that returns to the source. For the time it take for the signal to propagate down and back, the voltage applied to the source pin will remain mid-supply. This is very likely to create glitches on the clock being looped back into the SPI controller. These glitches may over-clock the state machine and cause unpredictable operation. Adding a series resistor allows the voltage to step beyond the switching threshold, which prevents glitches. A 33 ohm will allow the voltage to step further away from the switching threshold than the 22 ohm. Increasing the resistor too much will compromise clock transition time, which may impact performance. I would avoid going higher than 33 ohms unless you observe an issue where the step function on the signal is causing problems.

The signal trace that connects between the pin and resistor will create a similar step and this is unavoidable. However, the step will be filtered by the input buffer if short. This is why it is important to keep this trace short.

Hopefully, this explains why we require these resistors and why they need to be close to the source pin

Thank you for your answer.

I understand that it is important to make sure that:

-Wire the SPI_CLK signal as short as possible.

-Place a resistor of about 22 to 33Ω in series and measure the actual waveform to check if there is glitch or overshoot in the clock waveform.

In addition, noise radiation from this CLK line is currently our problem.

Is there any reduction method other than the following?

-Shorten the CLK line.

-Dull CLK by inserting a resistor or a capacitor on the order of pF.

-Lower the impedance of the power supply and signal ground.

Regards,

Sreenivasa

Hi Board designers,

Refer below for description about SPI signal series resistor use case (for understanding and can be applied for AM6x)

AM3358: A ringing problem of eMMC interface

I do not think the voltage change observed on the clock signal while it is high is causing your problem. It appears you are probing the clock signal near the eMMC device based on the shape of the clock signal rise/fall edges. You need to probe the clock signal near the processor. I suspect you will see a non-monotonic transition near mid-supply on the source end of the PCB trace. This non-monotonic transition is likely causing the problem.

The processor sources the clock out to the eMMC device and loops in back at the processor pin to improve timing margin. So there is a good chance the non-monotonic transition occurring at the source is creating a glitch on the clock that is looped back into the processor.

The AM335x schematic checklist tells you to install a 33 Ω series resistor on MMCx_CLK (as close to the processor as possible). I do not see this resistor in your schematic. This resistor is necessary to prevent this problem.

The capacitor is likely changing the signal distortion enough to make it work better, but it is not a good solution.

The resistor doesn't eliminate the non-monotonic transition. It shifts the voltage away from the input buffer switching threshold voltage, where it is less likely to create a glitch on the looped back clock going back into the processor. The only way to resolve the clock glitch issue is install a 33 ohm series termination resistor located very close to the AM335x pin. The trace length between the processor pin and the series resistor should be as short as possible.

AM3354: MMC clock timing

I did not see any de-coupling capacitors between on the AM335x VDDSHV4 power pin after low pass filter L704. Were these accidently omitted in the snapshots provided? If not, each power pin needs local de-coupling capacitors after their respective low pass filters.

I’m concern with the SD Card ground connections. Hopefully the SD Card VSS1 and VSS2 pins are connected directly to the same ground as the AM335x device. I assume the other grounds shown for the SD Card are simply the metal chassis ground and they are not part of the SD Card signal and power ground connections.

They should not be using a zero ohm resistor for R514. This should be a 22 - 50 ohm resistor. The MMC/SD host controller in AM335x loops the clock back at the pin to improve timing margin for the internal circuits. However, there is a negative side effect of implementing clock loopback on a pin. The clock signal will be distorted on the source end of a signal trace and a series resistor of 22 - 50 ohms is required to modify the signal distortion such that is does not create a glitch on the looped back clock signal.

I will explain what happens. The clock output buffer inside AM335x has a source impedance of about 30- 50 ohms and a typical PCB signal trace has a characteristic impedance in the range of 40 - 60 ohms. When the output buffer toggles the signal from low to high or high to low, the voltage of the pin which sits between the output buffer and the PCB signal trace will not transition to the expected voltage immediately. This is because the output buffer impedance and trace impedance create voltage divider that causes the pin to step to a mid-supply voltage for a short time. This step will last as long as it takes for the clock signal to travel down the PCB signal trace to the SD Card, where it encounters a high impedance load that creates a reflection that allow the voltage to increase to VDD or VSS. The amplitude of the mid-supply voltage step may be near the AM335x clock buffer input switching threshold, which allows noise to create a glitch on the AM335x internal clock. The series resistor raises the impedance of the PCB portion of the voltage divider such that the voltage at the pin steps above or below the switching threshold.

I suspect this is what is causing the instability and the reduced clock amplitude is contributing to the issue.

What you observe on this signal depends on where you connected the probe, the bandwidth of your probe/scope, and quality of your scope probe ground.

You will need a very high bandwidth probe and scope to observe short over-shoot, under-shoot, and non-monotonic events on the signal. I recommend using a low capacitance FET probe with a very-very short low loop inductance ground.

You will see a mid-supply step on the signal when probing near the source. This occurs because the output impedance of the MMC0_CLK output buffer, series termination resistor, and characteristic impedance of the PCB signal trace creates a voltage divider. The voltage divider output is applied to the source end of the PCB signal trace. This voltage propagates down the trace to the far end where it encounters a high impedance load which causes a in-phase reflection that returns to the source. Therefore, the voltage transition observed on the far end will be a continuous transition between VSS and VDD. The is not the case for the source end, as it steps to a mid-supply determined by the voltage divider values and the transition only continues to VDD or VSS once the reflection returns from the far end. You need to select a series resistor value that allows the MMC0_CLK pin to step through the voltage of (VDDSHV4 / 2) without pause. I suggest the step observed on the MMC0_CLK pin should be at least 200mv above (VDDSHV4 / 2) on the rising edge and at least 200mv below (VDDSHV4 / 2) on the falling edge.

Regards,

Sreenivasa

Hi Board designers,

Refer below for description about SPI

SPI_MISO_ voltage was dropped from 3.3V to 2V

Query

Customer connected ADC data output (MISO) to AM2432 through ISO7741 using SPI interface. The expected voltage level of SPI_MISO_ADC was 3.3V, however it dropped down to 2V.

Answer

I can only assume their software has configured pin A14 on the AM243x device as an output and it is in contention with the output of the ISO7741 device.

Have customer check the voltage of this signal while the AM243x is held in reset?

Have customer disable the AM243x output buffer by writing the appropriate value to the TXDIS bit in the respective PADCONFIG register during this condition to see if the signal voltage changes.

Result

Customer disabled TX_DIS then voltage level became normal.

Regards,

Sreenivasa

Hi Board designers,

Information related to clock pulldown

e2e.ti.com/.../faq-am625-what-s-the-purpose-for-the-pull-down-r-on-mmc_clk

May I know what the purpose for the pull down R on MMC_CLK signal on TI EVM? May I know what the purpose for the pull down R on MMC_CLK signal on TI EVM?

Most of the IOs associated with the AM62x device default to the off state, which means any attached device input without an internal pull resistor would be floating until software configures the pin to drive the signal. We use an external pull-down rather than an external pull-up since the clock signal is held in a low logic state when paused.

Because there are cases where the clock is stopped or paused in a low logic state and the pull-down option is consistent with this logic state.

Regards,

Sreenivasa

Hi Board designers,

Information related to clock measurement

What you observe on this signal depends on where you connected the probe, the bandwidth of your probe/scope, and quality of your scope probe ground.

You will need a very high bandwidth probe and scope to observe short over-shoot, under-shoot, and non-monotonic events on the signal. I recommend using a low capacitance FET probe with a very-very short low loop inductance ground.

You will see a mid-supply step on the signal when probing near the source. This occurs because the output impedance of the MMC0_CLK output buffer, series termination resistor, and characteristic impedance of the PCB signal trace creates a voltage divider. The voltage divider output is applied to the source end of the PCB signal trace. This voltage propagates down the trace to the far end where it encounters a high impedance load which causes a in-phase reflection that returns to the source. Therefore, the voltage transition observed on the far end will be a continuous transition between VSS and VDD. The is not the case for the source end, as it steps to a mid-supply determined by the voltage divider values and the transition only continues to VDD or VSS once the reflection returns from the far end. You need to select a series resistor value that allows the MMC0_CLK pin to step through the voltage of (VDDSHV4 / 2) without pause. I suggest the step observed on the MMC0_CLK pin should be at least 200mv above (VDDSHV4 / 2) on the rising edge and at least 200mv below (VDDSHV4 / 2) on the falling edge.

Regards,

Sreenivasa

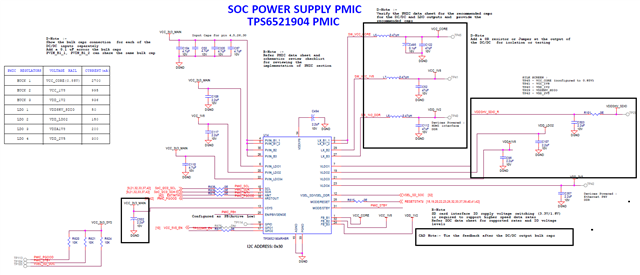

Hi Board designers,

PMIC capacitor and feedback recommendations

PMIC - feed back and jumper or 0R provisioning

Regards,

Sreenivasa