Hi,Experts

On page 128 of the datasheet,

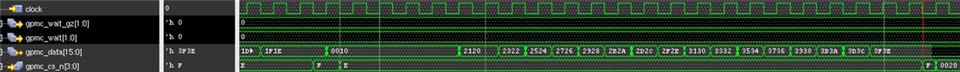

It is stated that the data changes from the rising edge of GPMC_CLK to D1, D2, and D3 with a delay of F15.

According to this, it seems correct that the other side (FPGA in our usage) should read data on the falling edge of GPMC_CLK.

<www.ti.com/.../66ak2g12.pdf

On page 1423 of the TRM.

It seems to me that it is correct to change data on the falling edge of GPMC_CLK and read data on the rising edge.

<www.ti.com/.../spruhy8i.pdf

In 66AK2G12, when GPMC Burst Write, does the value of D1, D2, and D3 change with the rising/falling edge of GPMC_CLK?

Best Regards,

Hidekazu