Other Parts Discussed in Thread: SYSCONFIG

Hi,

we are using the TMDS64GPEVM with the XAM6442A SFGGAALV SoC in combination with the MCU+ SDK 8.6.0.34. (SysConfig Tool 1.15.00)

All questions are related to applications running on the R5 only. (Bootswitches are set to NO_BOOT)

I have three questions:

1.

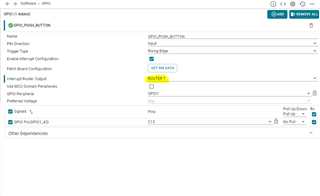

We realized that when we enable two GPIOs with interrupts, the Board_gpioInit is not able to succeed and exits with "SciClient event config failed". When we reduce the number of interrupts by one Board_gpioInit runs without errors. Is that a known issue and has something to do with our hardware and/or MCU+ SDK version?

2.

Board_gpioInit is not part of a public header of the autogenerated files. What is the reason behind it? I think to use for example interrupts we need to execute Board_gpioInit on startup.

3.

To start debugging on the R5 we use CCS 12.5.00. Here we launch the configuration and initialize R5 and M3 with the load_dmsc.js script.

We realized in case the application on the R5 crashes, we can't just reset the R5 core and start the application again. Here the Board_gpioInit fails again with "SciClient event config failed". We have to powercycle the board (I think to reset the M3 core) and to the described procedure again. Is that really needed or is there an alternative?

Thank you in advance.

Please come back to me in case anything is unclear.