Hi TI Expert.

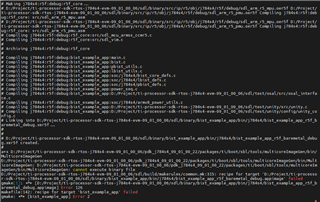

I am designing our functional safety system based on J721E. I read the information about BIST function and find an example in MCUSW.

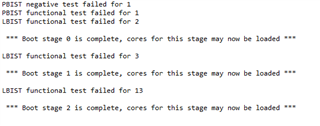

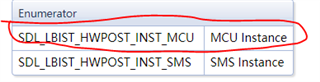

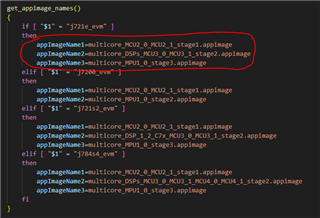

For my case, I used MCU1_0 as boot core, MCU1_1 as one safety channel, and one A72 as another safety channel. I learned that only BIST for MCU1_0 was started automatically and other cores (including MCU1_1 and Main Domian) need to be triggered by SW. Therefore, I refered to the example in MCUSW. But, I still have some questions.

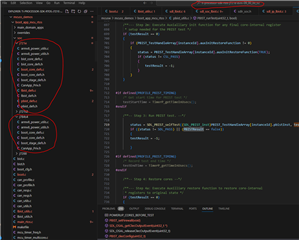

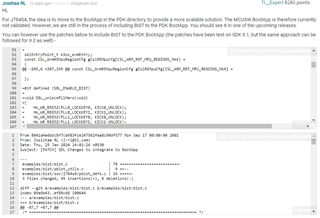

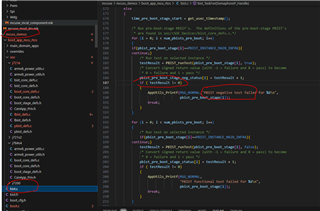

- In bist.c, what does "PBIST negative test" mean? Also, why to be wrong when "testResult !=0"? Pls refer to the picture.

- What is the difference between "PBIST negative test" and "PBIST functional test"?

- For the test result, can it be read by stage cores?

- For my case, because MCU1_0 is not functional safety channel, if MCU1_0 calls SDL to do BIST for MCU1_1 and A72, can it be ensured as the safety result to use?

Thanks

Dengkuan