Hi,

I would like to ask a question on EDMA on DM6437.

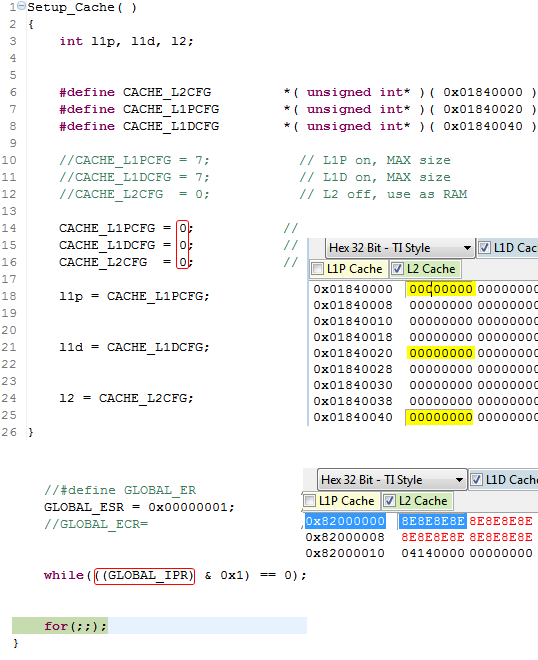

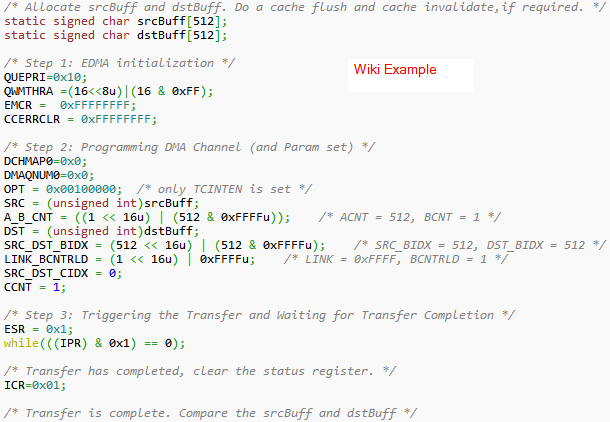

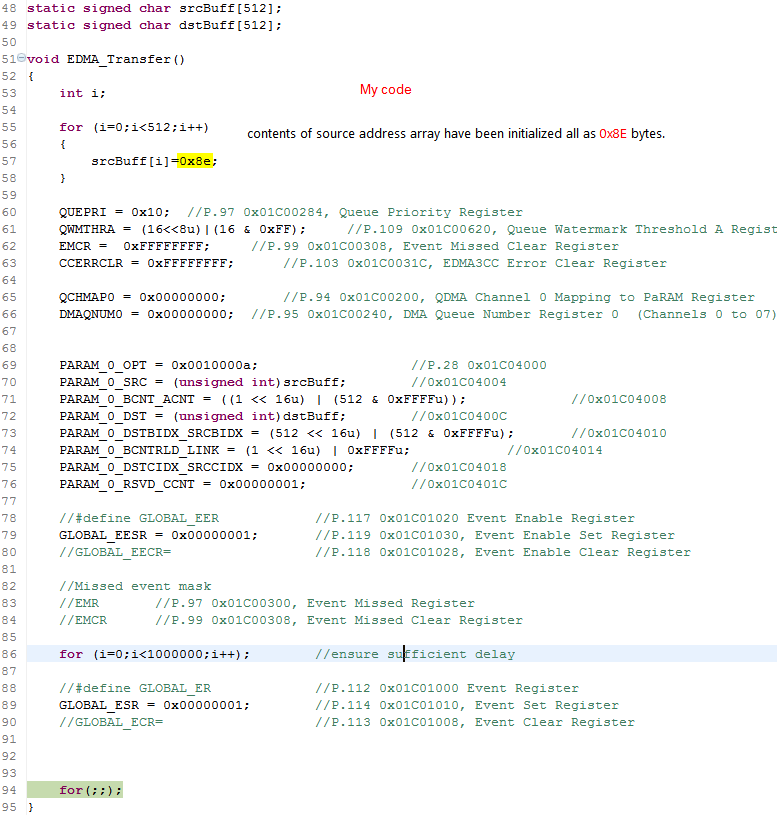

TI Wiki page Programming EDMA without EDMA3LLD package gave an example of configuring EDMA in the "hard manner" by modifying registers directly and I adapted the code into my DM6437 program:

Example code:

In my code,

However, when executing these code turns out to have no effect, and the content of srcBuff was not copied into dstBuff at all.

I have triple-checked register address and all of them are correct.

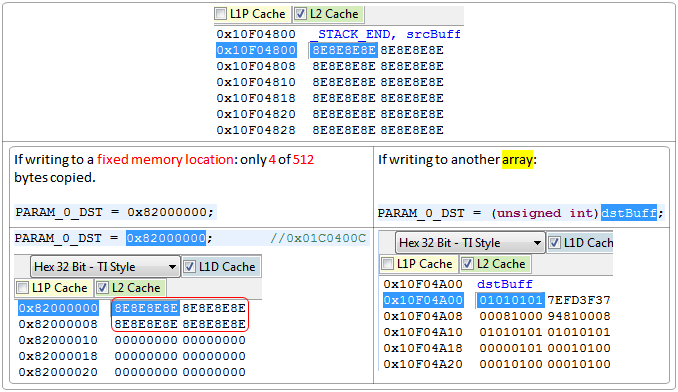

If instead of copying to dstBuff, I configure DMA destination to a fixed memory location, say, 0x82000000, then sometimes 0x8E would be copied to the destination array, but only for the first 4 entries; the remaining 512-4=508 entries remain unchanged. (1 )Changing 0x8E to other value, or (2) Changing destination to other fixed location, say, 0x83000000, resulted in the same that only first 4 out of 512 bytes are copied.

I would like to ask about:

1. Why for fixed location destination only 4 bytes are copied?

2. Why no copy occur when destination is set to dstBuff?

3. Did I miss any initialization register? Since I copied the Wiki example line for line, if I missed any register(s), does it mean the Wiki article also missed the same register(s)?

Thanks,

Zheng