Hi,Brijesh;

After adding the patch you provided, I have the following questions:

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi,Brijesh;

After adding the patch you provided, I have the following questions:

Hi xie jc,

Can you please read overlay managers registers and share them for the review? I think it uses DSS0_OVR4 overlay, so please save 20 registers from offset 0x04AD0000 and share them?

Regards,

Brijesh

Hi,Brijesh;

My SOC is TDA4VE. After running my test demo, the registers read are as follows;

| dss register | value |

| 0x0004AD0000 | 0x00000000 |

| 0x0004AD0001 | 0x00000000 |

| 0x0004AD0002 | 0x00000000 |

| 0x0004AD0003 | 0x00000000 |

| 0x0004AD0004 | 0x00000000 |

| 0x0004AD0005 | 0x00000000 |

| 0x0004AD0006 | 0x00000000 |

| 0x0004AD0007 | 0x00000000 |

| 0x0004AD0008 | 0x00000000 |

| 0x0004AD0009 | 0x00000000 |

| 0x0004AD000A | 0x00000000 |

| 0x0004AD000B | 0x00000000 |

| 0x0004AD000C | 0x00000000 |

| 0x0004AD000D | 0x00000000 |

| 0x0004AD000E | 0x00000000 |

| 0x0004AD000F | 0x00000000 |

| 0x0004AD0010 | 0x00000000 |

| 0x0004AD0011 | 0x00000000 |

| 0x0004AD0012 | 0x00000000 |

| 0x0004AD0013 | 0x00000000 |

thanks

Hi xie jc,

Can you please read each register at the offset of 0x4? This does not include regsiter at the offset 0x20, that' where the pipelines are enabled..

Regards,

Brijesh

Hi,Brijesh;

The registers read are shown in the table below.Please help me check, thank you

| dss register | value |

| 0x0004AD0000 | 0x00000000 |

| 0x0004AD0004 | 0x00000000 |

| 0x0004AD0008 | 0x00000000 |

| 0x0004AD000C | 0x00000000 |

| 0x0004AD0010 | 0x00000000 |

| 0x0004AD0014 | 0x00000000 |

| 0x0004AD0018 | 0x00000000 |

| 0x0004AD001C | 0x00000000 |

| 0x0004AD0020 | 0x00000000 |

| 0x0004AD0024 | 0x00000000 |

| 0x0004AD0028 | 0x00000000 |

| 0x0004AD002C | 0x00000000 |

| 0x0004AD0030 | 0x00000000 |

| 0x0004AD0034 | 0x00000000 |

| 0x0004AD0038 | 0x00000000 |

| 0x0004AD003C | 0x00000000 |

| 0x0004AD0040 | 0x00000000 |

| 0x0004AD0044 | 0x00000000 |

| 0x0004AD0048 | 0x00000000 |

| 0x0004AD004C | 0x00000000 |

Hi xie jc,

But there is no pipeline enabled here. Have you taken this register dump after or while running the application? All the registers shouldn't be zero if it is taking after running or while running the usecase?

By default, we use overlay4 for dss m2m node, so there should be some value set in the register at the offset 0x20 and 0x24.

Regards,

Brijesh

Hi,Brijesh;

Have you taken this register dump after or while running the application?

answer:Yes

My test application tivxDisplayM2MNode parameter configuration is as follows:

Hi xie jc,

But we typically use overlayid as 3, because that's the one reserved for the dss m2m node. Can you check it and then read the value of the overlay3 registers ?

Regards,

Brijesh

Hi,Brijesh;

When I used overlay id 3, it didn't seem to have any effect. The two images were simply overlaid, and didn't use alpha values to mix and overlay the two images. The captured registers are as follows:

| dss register | value |

| 0x0004AD0000 | 0x00000400 |

| 0x0004AD0004 | 0x00000000 |

| 0x0004AD0008 | 0x00000000 |

| 0x0004AD000C | 0x00000000 |

| 0x0004AD0010 | 0x0F00F00F |

| 0x0004AD0014 | 0x00000000 |

| 0x0004AD0018 | 0x00000000 |

| 0x0004AD001C | 0x00000000 |

| 0x0004AD0020 | 0x00000001 |

| 0x0004AD0024 | 0x00000005 |

| 0x0004AD0028 | 0x00000000 |

| 0x0004AD002C | 0x00000000 |

| 0x0004AD0030 | 0x00000000 |

| 0x0004AD0034 | 0x00000000 |

| 0x0004AD0038 | 0x00000000 |

| 0x0004AD003C | 0x00000000 |

| 0x0004AD0040 | 0x00000000 |

| 0x0004AD0044 | 0x00000000 |

| 0x0004AD0048 | 0x00000000 |

| 0x0004AD004C | 0x00000000 |

thanks

Hi xie jc,

ok from these registers, both the layers are setup correct as per the z-order.

Can you please check the value of global alpha value in both the video pipelines (VID_GLOBAL_ALPHA)? If the global alpha value is set to 0x0, can you please try setting it to 0xFF?

Regards,

Brijesh

Hi xie jc,

Can we please readback the register value and confirm the same in both the video pipelines?

Regards,

Brijesh

Hi,Brijesh;

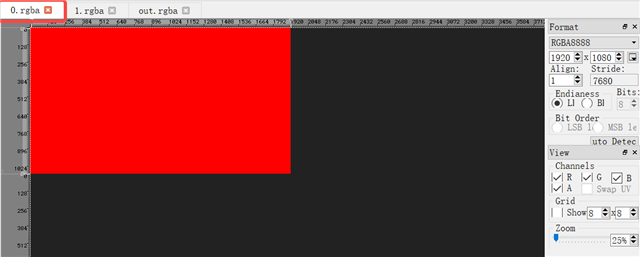

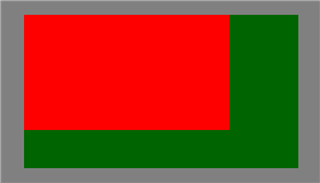

1、input image0 R=255 G=0 B=0 A=30

2、input image1 R=0 G=255 B=0 A=100

3、output image A=255

After overlaying two semi transparent images, the Alpha value has changed to 255, which looks abnormal. I need the semi transparent effect after overlaying.

Please help me solve this problem together, thank you.

Hi,

Sorry i did not get the above experiment. What is input image0 and image1? How are specifying alpha value for both of these images? Are they fed to different pipelines?

Can you please read the value of DSS0_VID_GLOBAL_ALPHA register for all video pipelines that you are using?

Regards,

Brijesh

Hi,Brijesh;

tivxDisplayM2MNode(vx_graph graph,

vx_user_data_object configuration,

vx_image input0,

vx_image input1,

vx_image output)

1、 What is input image0 and image1?

answer: input image0 and image1 Corresponding parameters for tivxDisplayM2MNode.

2、 How are specifying alpha value for both of these images?

answer:Use the following method to assign values to input image0 and image1 of tivxDisplayM2MNode.

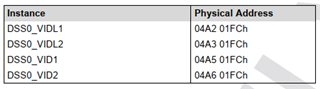

2、Can you please read the value of DSS0_VID_GLOBAL_ALPHA register for all video pipelines that you are using?

0x04A201FC:0x000000FF

0x04A301FC:0x000000FF

0x04A501FC:0x000000FF

0x04A601FC:0x000000FF

Hi xie jc,

This looks to be fine to me. i need to see in specs, if there is anything else missing. This should have worked fine.

Regards,

Brijesh

Hi xie jc,

What exactly image format you are using for both the input images, image0 and image1? i wanted to see what is set in the attribute registers for both these inputs pipelines and see if alpha is expected in the upper byte or lower byte?

Regards,

Brijesh

Hi xie jc,

ok, i see the problem. This format uses RGBX format in the DSS, which means it does not use alpha value from the pixels, instead it just treats as X, which is dont care. Alpha value is taken from the global alpha value, which is 0xFF, so it will make the layer as transparent.

Can you try a small change in tivxDisplayExtractFvid2Format API in the video_io\kernels\video_io\display_m2m\vx_display_m2m_target.c file, as shown below?.

case (vx_df_image)VX_DF_IMAGE_RGBX:

format->dataFormat = FVID2_DF_RGBA32_8888;

format->pitch[FVID2_RGB_ADDR_IDX] = (uint32_t)obj_desc_img->imagepatch_addr[0].stride_y;

break;

Regards,

Brijesh

Hi xie jc,

Are you sure that tiovx is rebuild and changes are in?

Can you please read ATTRIBUTE register for both the channels and share the value of it?

Regards,

Brijesh

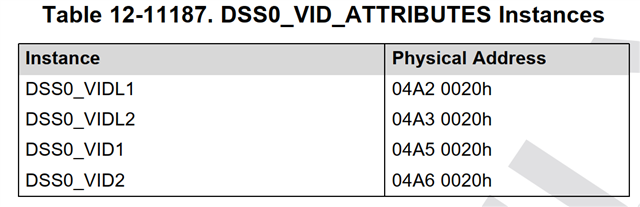

Hi,Brijesh;

1、Are you sure that tiovx is rebuild and changes are in?

>>>Yes,I am sure.

2、Can you please read ATTRIBUTE register for both the channels and share the value of it?

>>>As shown below

| dss register | value |

| 0x04A20020 | 0x00000000 |

| 0x04A30020 | 0x00000000 |

| 0x04A50020 | 0x00080011 |

| 0x04A60020 | 0x00080011 |

thanks

Hi,

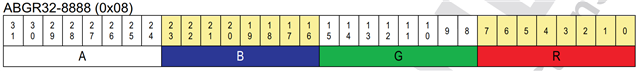

ok, can you please make sure that Alpha value is set in the MSB, as shown below?

Regards,

Brijesh

Hi,Brijesh;

can you please make sure that Alpha value is set in the MSB ?

>>>I've always done this before, and the image format for 'vxCreateImage' is 'VX_DF_IMAGE_RGBX'.

hi xie jc,

ok, it looks ok to me. Let me look at it again and see if there is anything else missing.

Regards,

Brijesh

Hi xie jc,

no yet, i will update you about it in this week.

Regards,

Brijesh

Hi xie jc,

Not yet, could not check it due to other issue, will check next week.

Regards,

Brijesh

Hi Adam,

We are using m2m node to overlay two buffer layers, not a simple format conversion, okay? The patches used are as follows: