Hello TI Support Team,

we are using the AM6442A chip.

We want to read one word from the GPMC interface in synchronous mode.

We have configured single synch read mode.

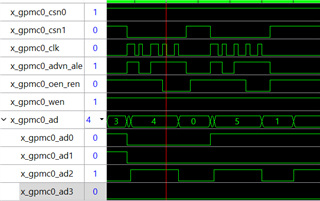

But the GPMC interface always wants to read two words (two GPMC clocks are active if /ren is low, see the following diagram).

basic parameters:

CSL_GPMC_CONFIG1_WRITEMULTIPLE_WRSINGLE

CSL_GPMC_CONFIG1_ATTACHEDDEVICEPAGELENGTH_SIXTEEN

CSL_GPMC_CONFIG1_DEVICESIZE_SIXTEENBITS

CSL_GPMC_CONFIG1_DEVICETYPE_NORLIKE

CSL_GPMC_CONFIG1_WRAPBURST_WRAPNOTSUPP

used delays not all, other delays are zero

ADVONTIME 1

ADVWROFFTIME 2

ADVRDOFFTIME 2

RDCYCLETIME 5

ne clock less tha

RDACCESSTIME 4

CSRDOFFTIME 5

OEONTIME 3

OEOFFTIME 5

WRCYCLETIME 5

WRACCESSTIME 4

CSWROFFTIME 5

WEONTIME 3

WEOFFTIME 5

WRDATAONADMUXBUS 3

PAGEBURSTACCESSTIME 1

CYCLE2CYCLEDELAY 2

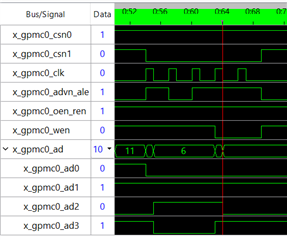

Single Synch 16 Bit read does a 2 x 16bit read instead of 1 x 16bit

(two GPMC clock rising edges are seen if /ren is low).

The delays i think are ok.

The tests are done with a single 16 bit access in the CCS debugger.

similar to:

uint16_t val;

uint16_t* wrRdPtr;

wrRdPtr = 0x051000000 //we use CS1

val = *wrRdPtr; -> GPMC does two 16 bit read accesses!!!

It is possible to configure the GPMC interface in single synch read mode to read only one word (1 x 16 bit read access) in NOR mode (we use a fpga no NOR memory)?

If multiple read is active (burst is activate) it reads always 2 words in one read cycle.

Writing of one word is ok. GPMC limits the single write to 1 x 16 bit, (only one rising edge if /wen is low) and is ok.

With best regards

Steffen