Other Parts Discussed in Thread: TDA4VM, AM68

Dear Team,

please can you point us where can we get the app mote from the linked thread?

"A similar app note is under development for Jacinto 7 Family of SoCs. "

Best Regards,

d.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

We do not have a hardware design guide for AM68A devices, but we do have several examples and application notes to help:

EVM design available for you to follow as a guide: www.ti.com/.../SK-AM68

LPDDR4 Application Note: https://www.ti.com/lit/pdf/spracn9

High Speed Signals Application Note https://www.ti.com/lit/pdf/spracp4

Sch Checklist: https://www.ti.com/lit/pdf/sprad91

Two different Power application notes: https://www.ti.com/lit/pdf/slvuci2 and https://www.ti.com/lit/pdf/slda060

Dear Robert,

thank you for the feedback.

We are aware of the app note that you provided.

Does this mean that the app note mentioned in the following thread is still under development for Jacinto 7 Family of SoCs?

Or does it only apply to TDA4VM?

Best Regards,

d.

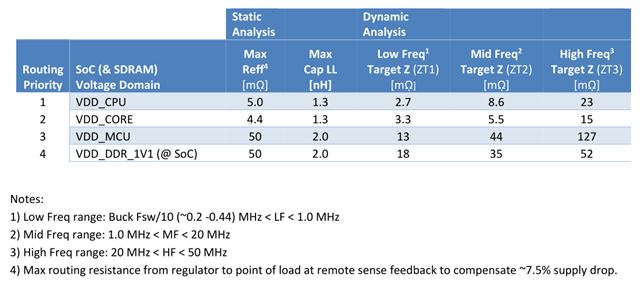

We do have PDN targets for each Jacinto7 device. For AM68, here are the targets. I thought documented in device data manual, but I didn't see them.

Regarding the decoupling capacitor strategy, I recommend following the EVM. I'm not aware of an application note similar to that discussed i the other E2E thread.