Other Parts Discussed in Thread: CLOCKTREETOOL, SK-AM64B, TMDS64EVM,

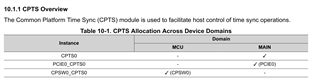

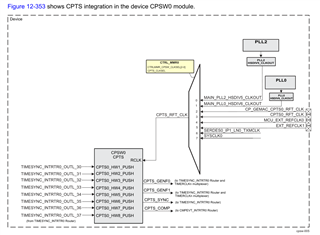

I am working on a CPST driver customisation for the AM642.

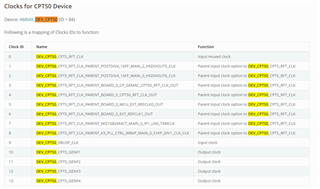

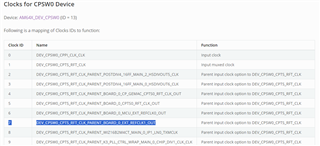

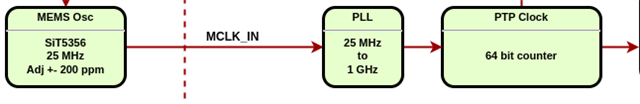

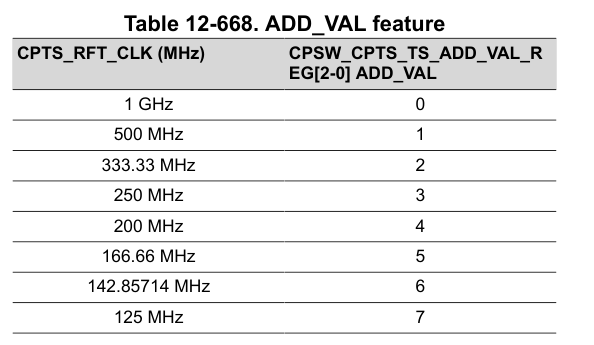

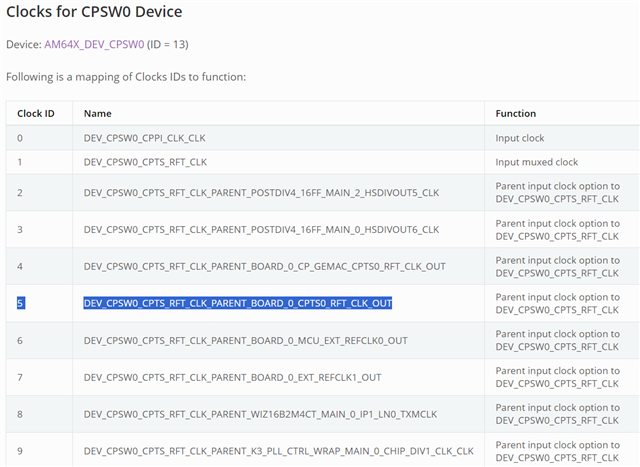

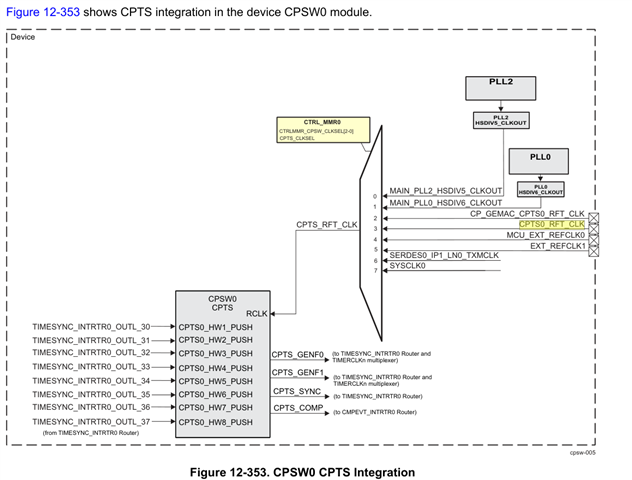

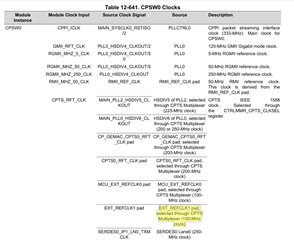

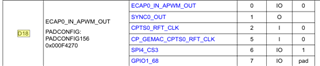

I want to use the EXT_REFCLK1 pin as source for the cpts_rft_clk via the CTRLMMR_CPTS_CLKSEL register. According to the documentation it should work and also with the CLOCKTREETOOL it seems to be possible. Please correct me if this is wrong. The idea behind this is to use the clock on EXT_REFCLK1 for PTP synchronisation.

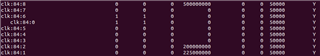

With devmen2 I can set it to the desired value.

Now I have looked in linux -Code (diver/net/ethernet/ti/am65-cpts.c and devtree for a support for this but unfortunately not found. Now my question, have I overlooked this and is there an easy way and what is the recommended way?

Thanks and best regards