Hello,

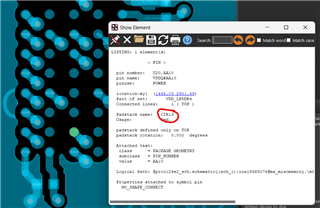

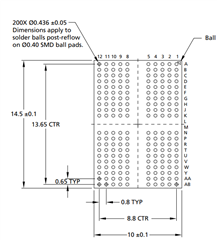

I'm referring to PROC124E2A AM62x-LOW POWER SKEVM, which uses MT53E1G16D1FW-046 WT:A LPDDR4. According to datasheet the size of the solderballs should be 0.436mm and PCB board uses 13mils(0.3302mm).

Also, if you see the spacing between two pins (0.65-0.436 = 0.214 mm = 8mils). Even if we choose a minimum trace width of 3mils, there is not enough space between the trace and pins.

Why was the pin diameter reduced and were there any consequences because of this?

Thanks

Santosh