Hi support team.

We are using the AM62x processors in our products and are facing the following issues.

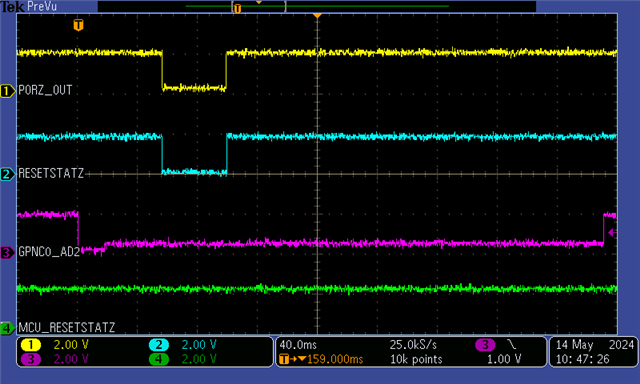

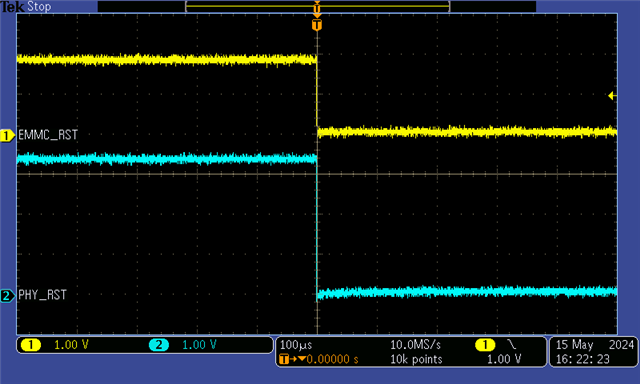

When SoC goes into DeepSleep mode the RESETSTATz output of the SoC is pulled down and puts the peripheral devices like Ethernet PHY, eMMC, DSI to LVSD bridge, etc. into the RESET state. This behavior creates issues on the SW side when SoC returns from the DeepSleep mode to the Active mode.

Is there any way to prevent the RESETSTATz pin from pulling down when the SoC goes into DeepSleep mode?

Or maybe there is a way to indicate that SoC is in a DeepSleep mode? As an example maybe some GPIO or Power rail is switched off. I could use this signal to block the Reset signal to peripheral devices when the SoC goes into DeepSleep mode.

On our products, we use the RESET schematic similar to the BeaglePlay Single Board Computer (based on the AM62x SoC).

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.