Hello TI,

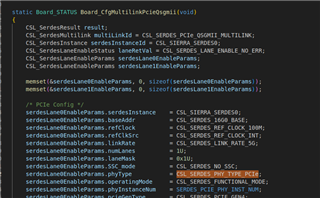

I am configuring SerDes 3 with PCIe 3. In our board only Lane 0 is connected to the FPGA, but when I configured only Lane 0, the PCIe doesn't get a link up. When I enable both lanes, then it works. Why does this happen? Is there a way that I can have only Lane 0 enabled?

Thank You,

Marina Lenza