Other Parts Discussed in Thread: TDA4VM

Hi :

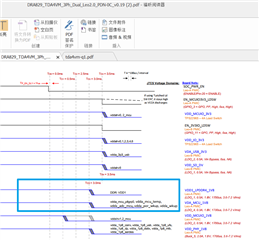

May I ask the power-off timing of TDA4VM? For example, the power supply DDR:VDD1 starts power-off at 3ms, does the voltage need to drop to 0V before 3.5ms? There are more capacitors in the actual power supply, and the power supply voltage cannot be dropped completely within 500us in the power-off timing we tested.

For example, in the timing of the data sheet, the Core power starts to drop at T2, but the capacitance of the Core power is very large, and the Core voltage must not fall to 0V at 3ms, so does this meet the requirements of the power-off timing?