Other Parts Discussed in Thread: SK-AM64B, AM6442

Tool/software:

Hi

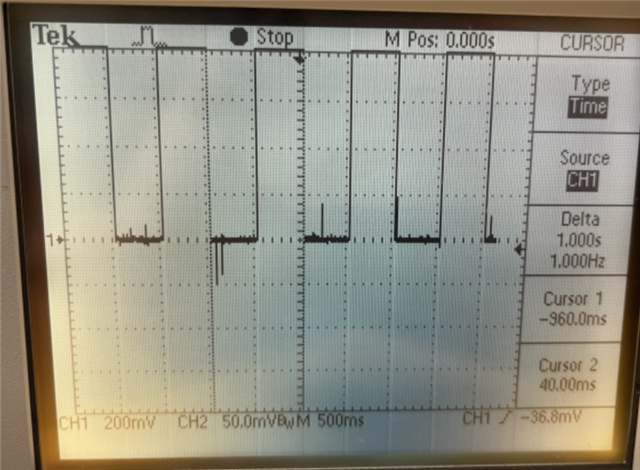

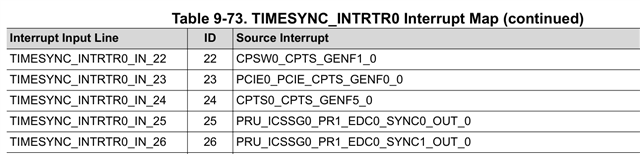

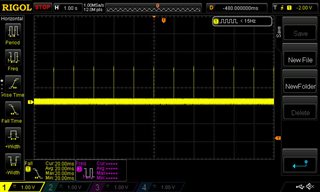

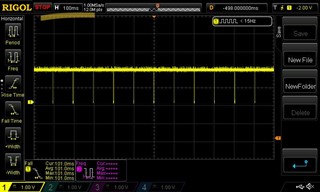

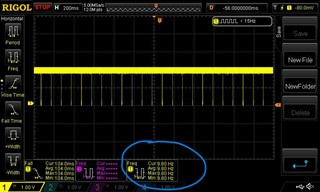

We observer some strange frequency of PPS after re-enbaling ( echo 1 > /sys/class/ptp/ptp0/pps_enable; echo 0 > /sys/class/ptp/ptp0/pps_enable; echo 1 > /sys/class/ptp/ptp0/pps_enable). The singal is measured on GPIO1_37 (V5) output.

Why is it so?

You might see that after re-enabling PPS signal signal period is about 100 ms.s.

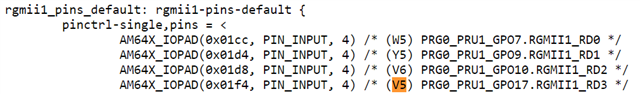

In device tree we have such a configuration:

&cpsw3g {

pinctrl-names = "default";

pinctrl-0 = <&cpsw_mdio0_pins_default

&rgmii1_io_bus_pins_default

&rgmii2_service_pins_default

>;

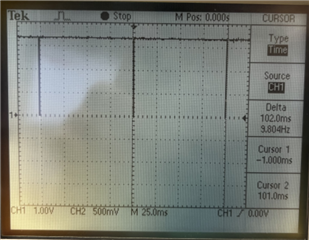

cpts@3d000 {

ti,pps = <7 1>;

};

};

#define TS_OFFSET(pa, val) (0x4+(pa)*4) (0x10000 | val)

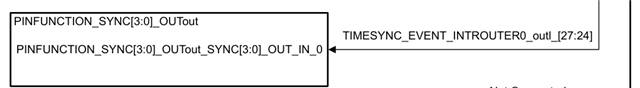

×ync_router {

pinctrl-names = "default";

pinctrl-0 = <&mcu_cpts_pps>;

/* Example of the timesync routing */

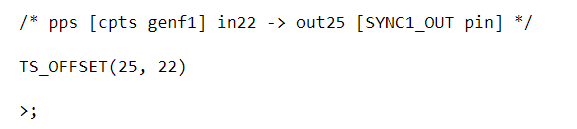

mcu_cpts_pps: mcu-cpts-pps {

pinctrl-single,pins = <

/* pps [cpts genf1] in22 -> out37 [cpts hw8_push] */

TS_OFFSET(37, 22)

/* pps [cpts genf1] in22 -> out25 [SYNC1_OUT pin] */

TS_OFFSET(25, 22)

>;

};

};