Other Parts Discussed in Thread: DXP

Tool/software:

Hi,

We are trying to connect a new sensor to our phytec AM62A board. What is the best way to debug this process? The sensor driver is created, and we see the video device in linux (visible with media-ctl and v4l2-ctl).

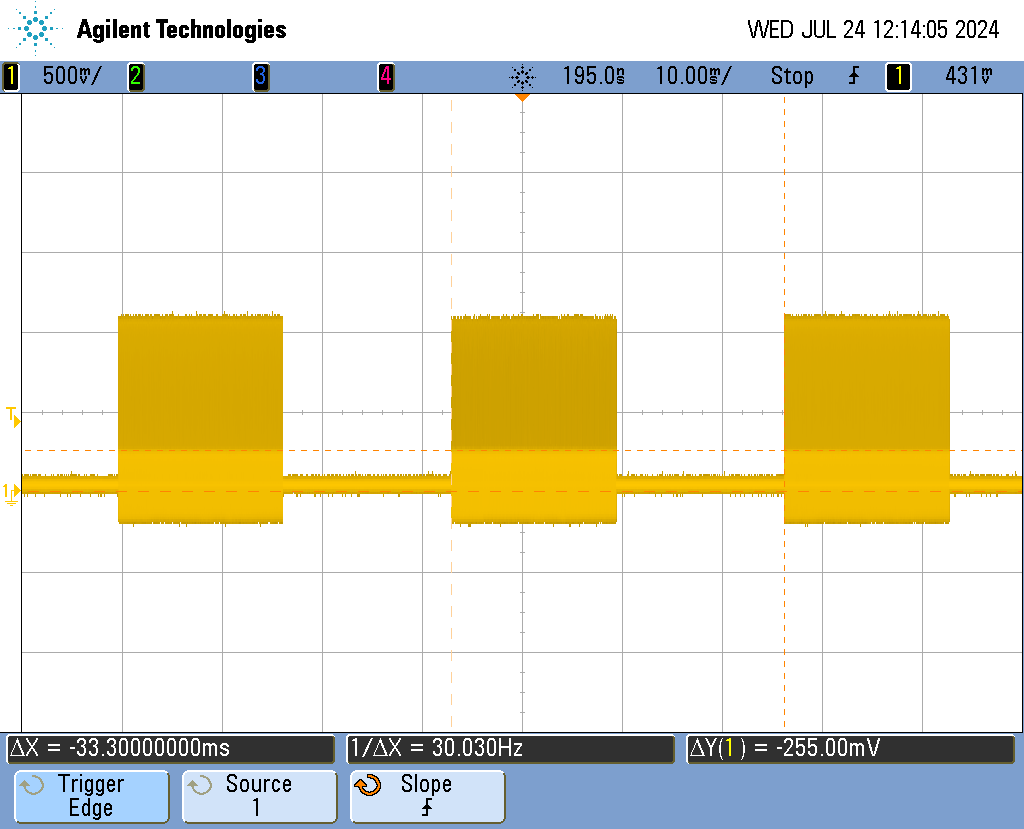

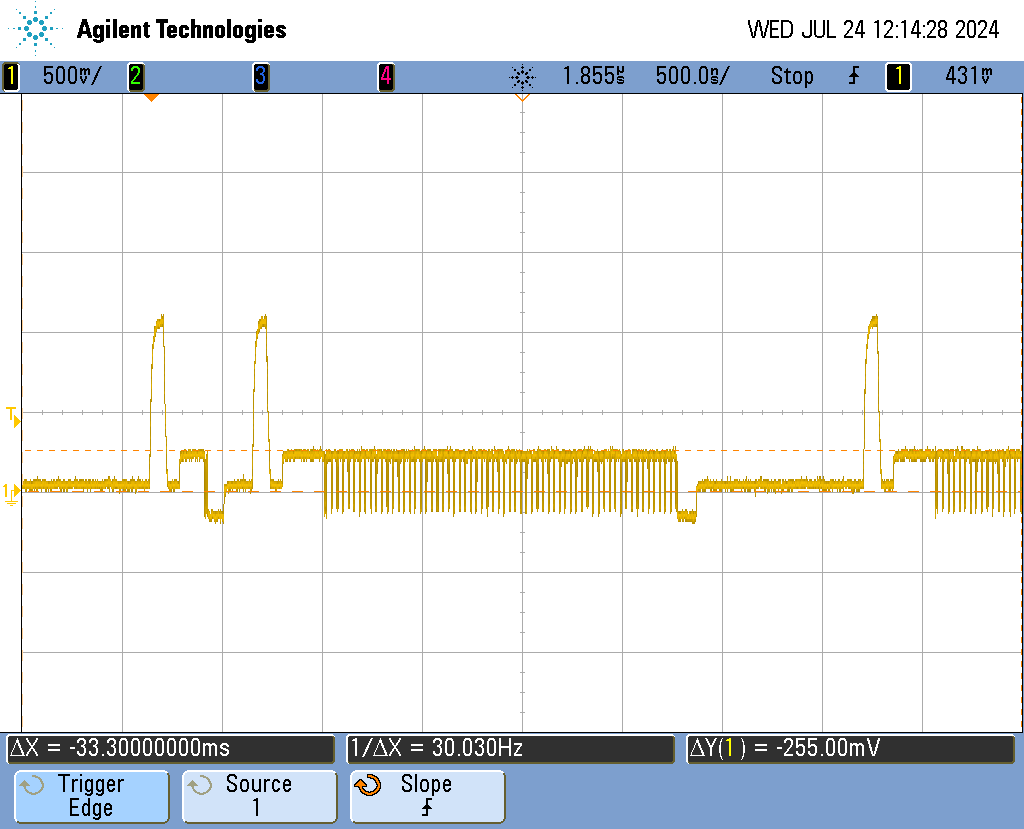

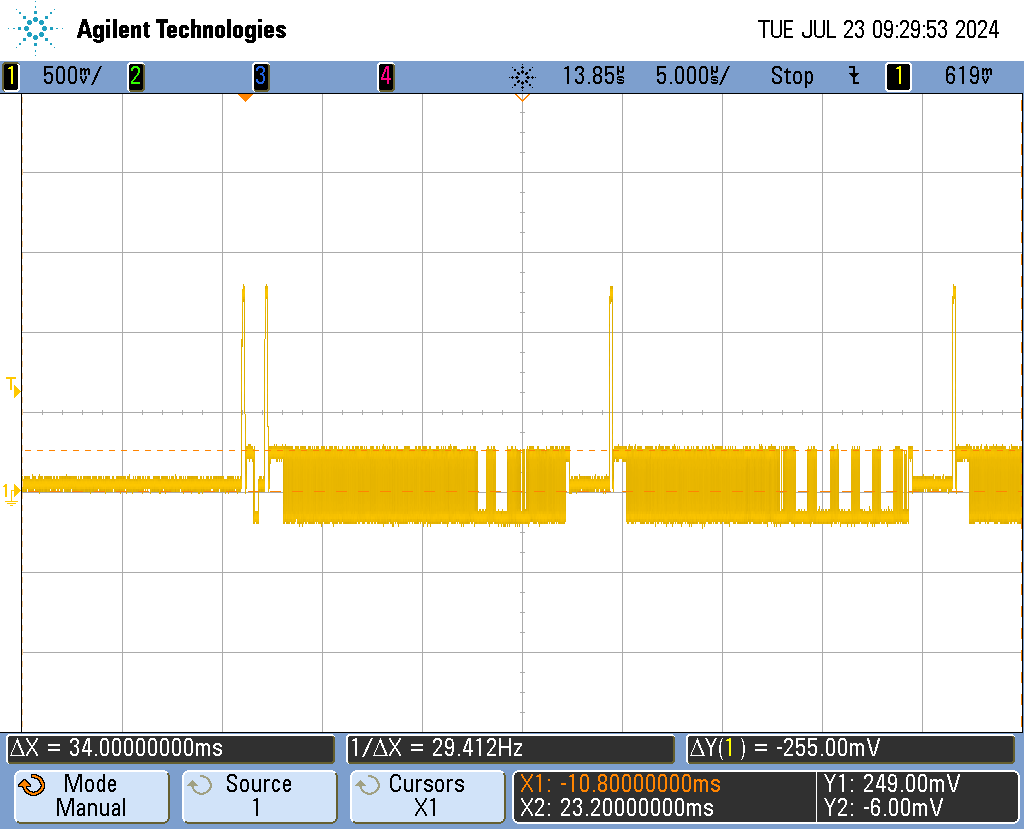

We have clock and data available on the CSI-2 lines, and those look ok, but when using v4l2-ctl -d 3 --stream-mmap we only get a frame rate of 0.2 fps instead of the 30 that we expect.

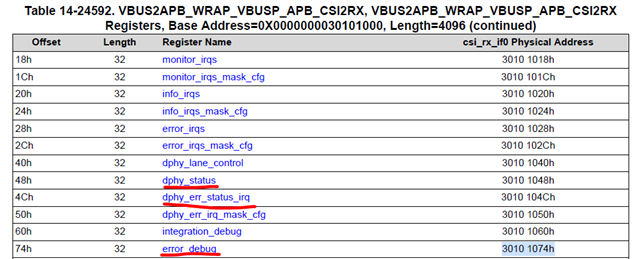

Is there a way to see what is going on underneath, whether packets are being discarded and if so, why, etc?

Thanks,

Bas Vermeulen