Tool/software:

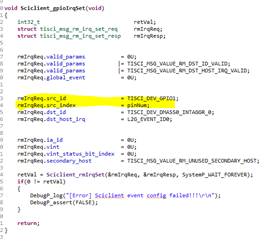

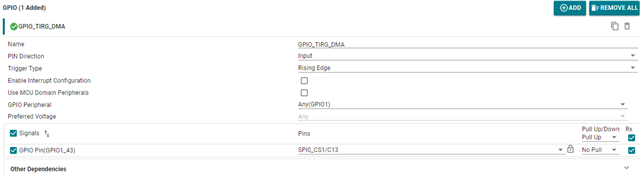

Follow the example project, trigger DMA with the help of GPIO on AM64x devices.

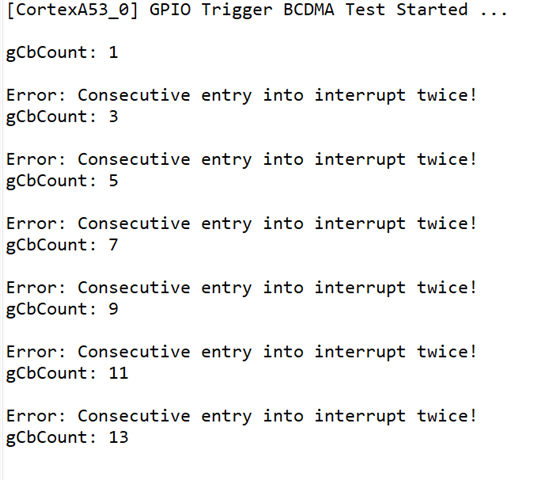

During the debugging process, it was found that a single change in GPIO level triggers two DMA interrupts.

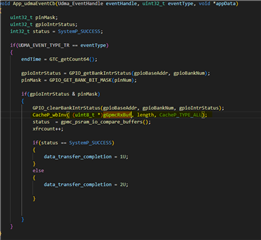

After completing one conversion, refreshing the cache for DMA-related variate temporarily resolves this issue.

However, I cannot confirm that this approach addresses the issue comprehensively.