Tool/software:

Setup :

Board : J784s4_evm

Test on processors R5F : mcu2_0, mcu2_1, mcu3_0, mcu3_1, mcu4_0 and mpu : A72 in SD card boot mode

SDK version : 9.01

Processors OS : linux , FreeRTOS

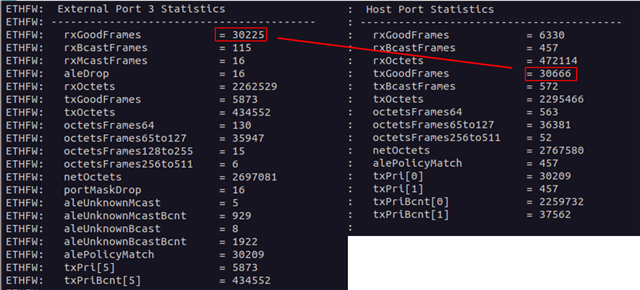

Test : Testing flow control inside the CPSW9g.

Context :

Hello Ti members,

I'm evaluating the Ethernet options inside of the Jacinto Soc with the board J784s4_evm. The documentation SPRUJ52C l.1327 talk about the flow control inside the CPSW9g.

I want activate this option by setting to 1 the variable XGE_CPSW_PN_MAC_CONTROL_REG_RX_FLOW_EN and TX respectively, along side the ethfw.

I believe the commands to add in the cpsw_macport.c are :

CSL_FINS(macControl, XGE_CPSW_PN_MAC_CONTROL_REG_RX_FLOW_EN, 1U);

CSL_FINS(macControl, XGE_CPSW_PN_MAC_CONTROL_REG_TX_FLOW_EN, 1U);

CSL_FINS(macControl, XGE_CPSW_PN_MAX_BLKS_REG_RX_MAX_BLKS, 2U);

CSL_FINS(macControl, XGE_CPSW_PN_MAX_BLKS_REG_TX_MAX_BLKS, 2U);

But in the same document I have found this l.1437 :

/* Clear fields not supported by hardware */

CSL_FINS(macControl, XGE_CPSW_PN_MAC_CONTROL_REG_EXT_RX_FLOW_EN, 0U);

CSL_FINS(macControl, XGE_CPSW_PN_MAC_CONTROL_REG_EXT_TX_FLOW_EN, 0U);

The variable is almost similar to the one I want to activate so it interrogate me.

What is this variable ? Why is it not supported and is it linked to the flow control inside the switch ?

Thank you in advance, and if you have any question, please ask.

Regards,

Matthias