Tool/software:

Hi there!

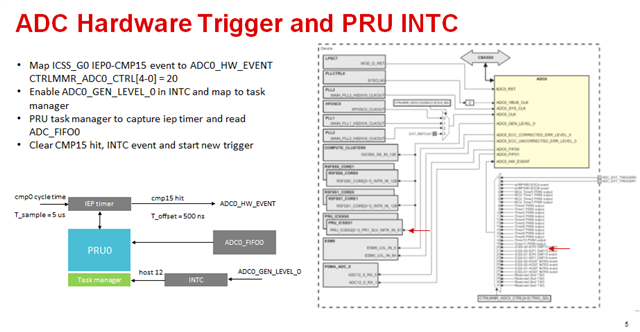

Is there an example to access the internal ADC from the PRU?

Regards.

PS: We can read from the R5F in a high priority thread, but we would have to get PPS and sync clocks with the PRU and since we solved this already for PRU with your help, we're considering the first alternative. That is, sampling with the same PRU_ICSSG.