Other Parts Discussed in Thread: SK-AM62, SK-AM62B

Tool/software:

Dear TI experts,

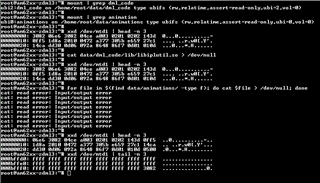

Our AM62x system using multiple MTD partitions for Bootloaders, Kernel, Data, etc. We recently met an issue that when we read a file from Data mount point, there's an IO error and every MTD partition left shifted by 2 bytes. After rebooted, data dumped from partitions became valid again and issue still occurred. The creation of UBIFS have no error.

After more evaluation, we found that turning off a mount option makes the reading of that file did not cause any error, but reading other file make it appeared again.

Detail:

I/O error when I read a file, causing MTD partitions' data shifted.

Turn off bulk_read option, reading above file not caused any error but error when I read other file:

My question is:

- What is possibly causing this issue? (Dumping MTD partition using `xxd` command is fine but reading a specific file make every MTD partition shifted 2 bytes)