Part Number: AM62A7-Q1

Tool/software:

Hi

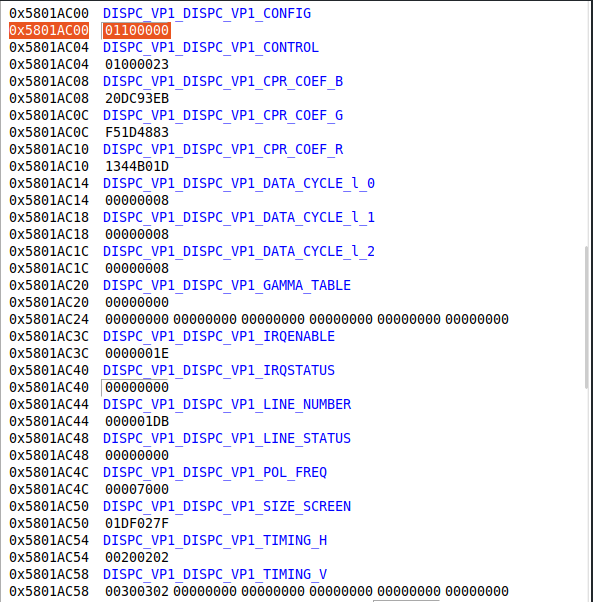

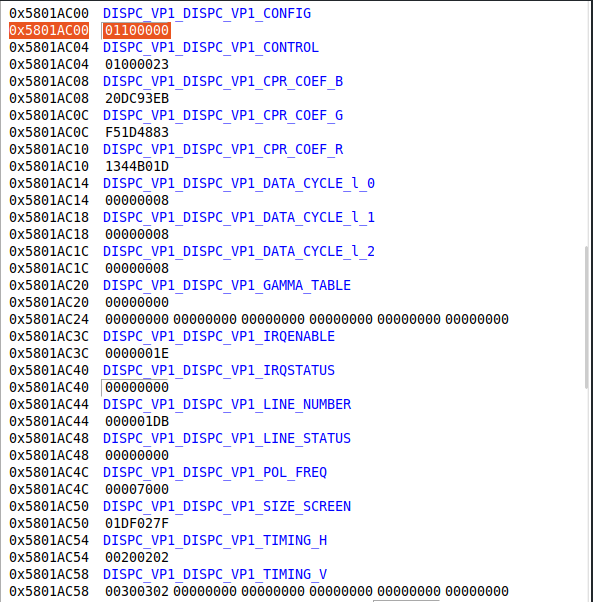

we are doing lcd video output with below VP settings

The default setting is progressive.

What part should I modify to change it to interlace?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: AM62A7-Q1

Tool/software:

Hi

we are doing lcd video output with below VP settings

The default setting is progressive.

What part should I modify to change it to interlace?

Hi,

Here is the TRM snippet from the DSS chapter:

Each VP output can be configured in progressive output mode or interlaced output mode. The selection is done by writing into the bit-field DSS0_VP_CONFIG[22] OUTPUTMODEENABLE register bit. The default setting is for progressive mode.

Regards,

Krunal

Hi,

I changed the values by referring to TRM, but there was no change in the video.

Can I just change the values?

Regards,

Kim

Hi

We are outputting progressive 640x480 BT656 Progressive format output from the camera to the LCD.

The LCD setting is set to Interlace and we are testing it.

devmem2 0x3020b000 w 0x01500000

We are proceeding with the AM62A register setting value, and the screen appears as below.

There was no change in the output even after applying the value.

If the LCD setting is set to Progressive, it appears as in the image below.

Is there anything else I need to set up?

Regards,

Kim

Hi Kim,

It appears that the config register is a shadow register and you need to configure the go bit. I am wondering if you set the gobit after configuring to progressive mode.

Regards,

Krunal

Hi,

devmem2 0x3020b004 w 0x01000002

devmem2 0x3020b000 w 0x01500000

devmem2 0x3020b004 w 0x01000023

As above, gobit is set at the end.

Are the above settings wrong?

Regards,

Kim

Hi Kim,

I am not sure I understand your value for 0x3020b004, what's the default value for that register? For example, on TI EVM with Linux it's 0x341. The value makes sense because all the formats, VP modes are enabled.

Try the following simple test:

devmem2 0x30208000 w 0x2

devmem2 0x3020B004 w 0x361

Do you see a colorbar appear on your monitor?

Regards,

Krunal

Hi, Krunal

I checked the colorbar image.

However, when running it with videotestsrc, it is still not output properly.

So I changed vertical from 480 -> 240 in the panel-simple code and checked the normal output of the image.

Is this property used in tidss_dispc?

If not, where is it referenced?

Regards,

Kim

Hi Kim,

Yes, TIDSS will yse your panels-simple timing and I am assuming you have a proper compatible field set in the DT.

Regards,

Krunal

Hi, Krunal

I checked the video output after changing the vdisplay property to 240, but this was confirmed after changing it from 480 -> 240 using the gstreamer videoscale option.

After the change, the screen appears well, but there is a difference on the screen due to videoscale interpolation.

gst-launch-1.0 videotestsrc pattern=circular ! video/x-raw, width=640, height=480 ! videoscale ! video/x-raw, width=640, height=240 ! kmssink driver-name=tidss sync=false

We want to output the final video as 480 without using gstreamer videoscale.

Is there a way?

Regards,

Kim

Hi Kim,

I am not sure I understand what you are requesting for? The panel width and height properties are defined in panel-simple file and do you not see that being reflected? What does kmsprint show?

Regards,

Krunal

Hi, Krunal

We are currently receiving input as 640x480.

If we set the output to interlace, is it correct to set it to 640x240?

Regards,

Kim

Hi Kim,

You should always program the DSS to match your LCD specs. If your input and output is of not same resolution you may need to use videoscale.

Regards,

Krunal

Hi, Krunal

The LCD is set to 640x480.

I think that even if use interlace, don't need to scale it to 240.

Is that right?

Regards,

Kim

Hi Kim,

If LCD is set to 640x480 then why does kmsprint show 640x240?

Regards,

Krunal

Hi Krunal

The mode name is 640×480 interlace mode.

When I set the interlace register in am62a and output it as 480, the LCD screen did not output properly.

So I checked the normal output when I changed it to 240.

I think 240 outputs even and odd values respectively. However, when I need to output it through tidss, it does not support interlace, so I think I need to scale 480 to 240 to output it.

Is that right?

Regards,

Kim

Hi Kim,

Let me check internally on the interlace mode settings because I am not sure why you need to program 240 instead of 480.

Regards,

Krunal

HI Krnnal

I also do not have any knowledge about interlace settings.

However, I confirmed that vdisplay (height) is halved when setting interlace in other soc (tda series) rtos settings.

The relevant registers are as follows.

devmem2 0x3020b050 w 0x00EF027F

I confirmed that the vdisplay value in panel-simple.c affects the SCREEN_SIZE register in tidss_dispc.c.

However, when the panel-simple vdisplay value was set to 240, the drm connector and crtc values were also set to 240. So, outputting to 480 was not possible.

I also want to know how to set it to 480 and output it.

Regards,

Kim

Hi Kim,

What's the reason for configuring to interlace settings? Unfortunately, whatever you set as panel-simple that will be used by DRM as well. My assumption is we don't have support for interlace in driver but let me confirm internally and get back to you.

Regards,

Krunal

Hi Krunal

Unfortunately, the project we are working on requires interlacing.

Regards ,

Kim

Hi Kim,

Our driver does not seem to support interlace and I am checking with our IP team on the height/2 behavior.

Regards,

Krunal

Hi, Krunal

Could you please let me know the results of the IP team?

Regards,

Kim

Hello Kim,

Krunal is out of office for the rest of this week. Feel free to ping the thread if you do not get a response by Sept 25.

Regards,

Nick

Hi,

Based on my discussion with IP team, we do support interlace settings but you shouldn't have the need to half the values. It seems like our driver does not support interlace settings and I have filed an internal ticket for our team to review the requirement.

Regards,

Krunal

Hi,

So does that mean interlace output is currently impossible via the tidss driver?

Regards,

Kim

Hi Kim,

It's a feature we have not tested since our EVM only supports progressive mode.

Regards,

Krunal