Other Parts Discussed in Thread: SK-AM62-LP, SK-AM62A-LP

Tool/software:

Hi

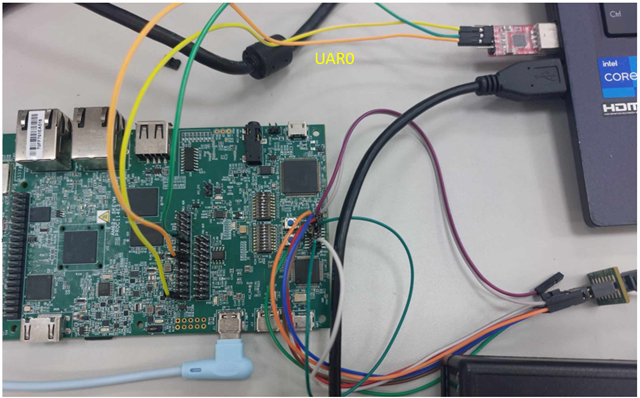

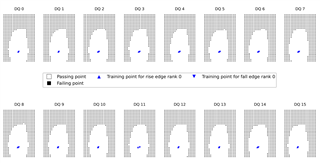

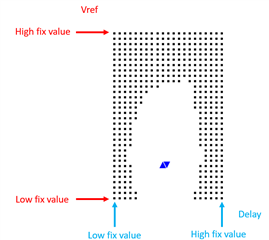

I want to use the DDR Margin Test Tool on the AM62x-SK-EVM for testing, but I encountered an issue in the red step while following the readme.txt instructions.

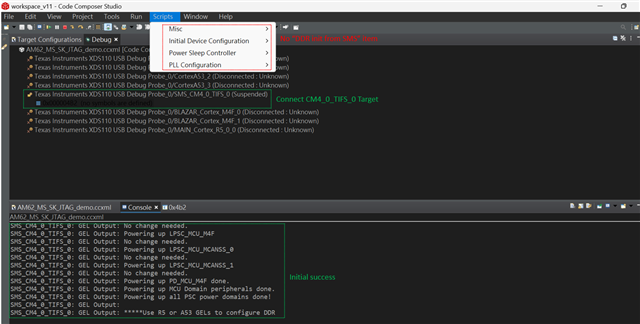

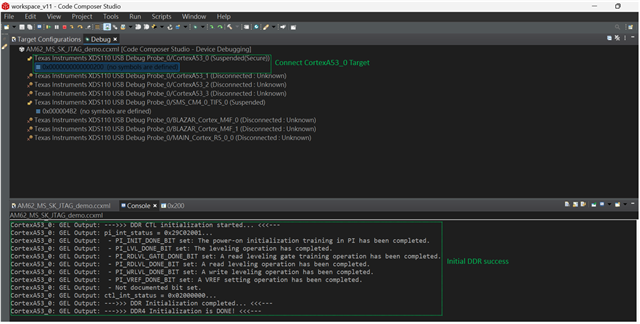

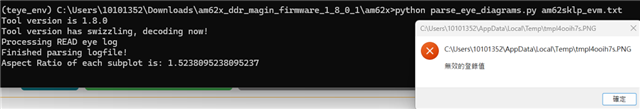

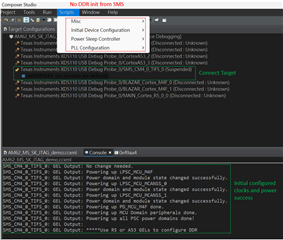

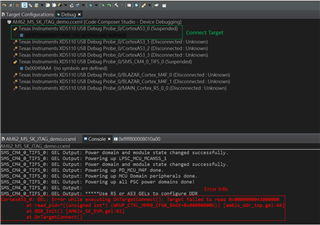

Steps 1 to 4 executed normally, but I encountered issues with Step 5, Step 6.a, and Step 6.b. as shown below.

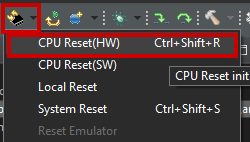

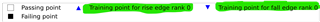

Step 5: Did not see the option "DDR int from SMS".

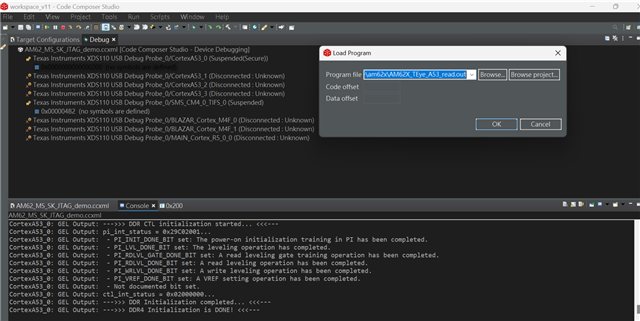

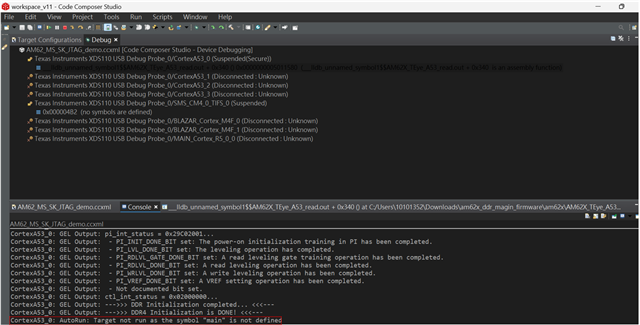

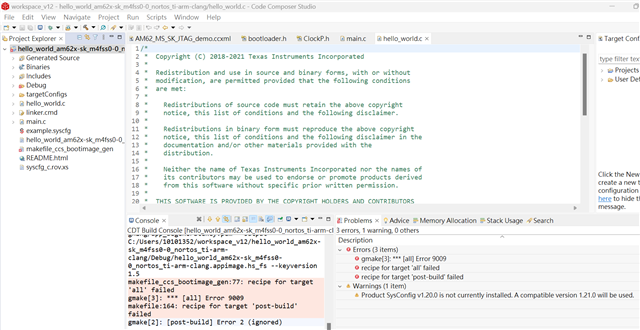

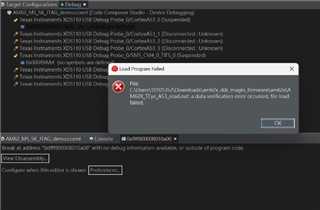

Step 6.a: When selecting to connect to CortexA53_0, an exception warning occurs as follows.

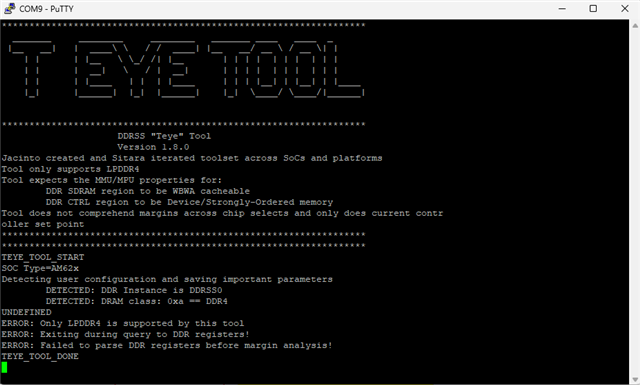

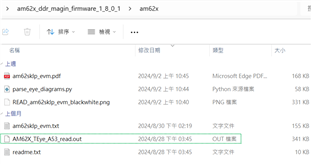

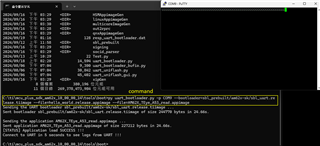

Step 6.b: Selecting the margin test file AM62X_TEye_A53_read.out results in a loading failure.

Could explain what issues I might be encountering?

sincerely grateful

P.S : DDR Margin Test Tool link: https://www.ti.com/tool/download/DDR-MARGIN-FW/1.8.0