Tool/software:

Hi experts

Now we are using the AM62P52 to develop our product, and we have completed the layout.

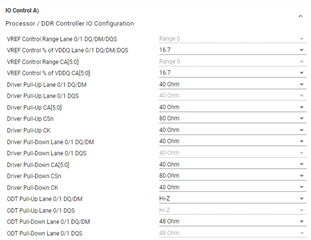

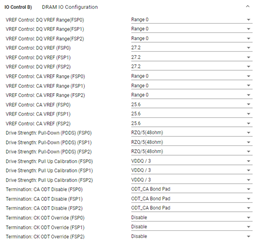

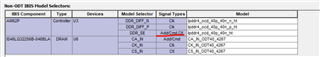

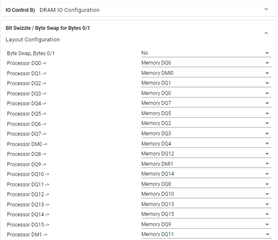

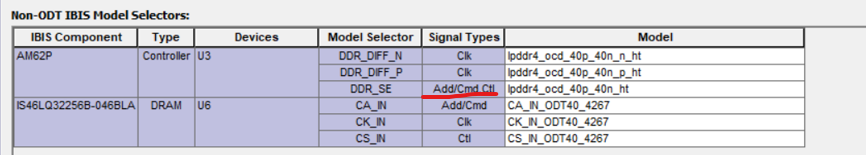

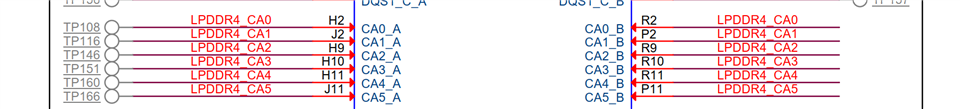

What is troubling us now is how to adapt the configuration parameters in the AM62Px DDR subsystem to the simulation parameters in Hyperlynx, as shown in the figure below. Is there a simulation guide that can be provided to us? Thank you!