Tool/software:

Hello,

I would like to simulate HS200 mode in write phase.

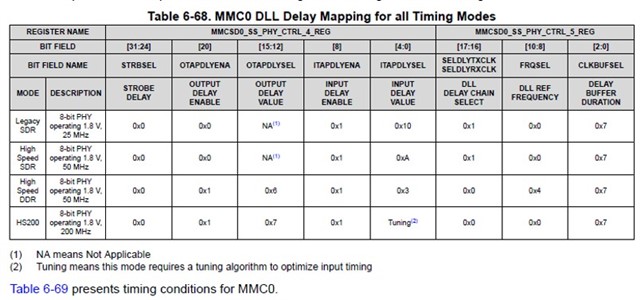

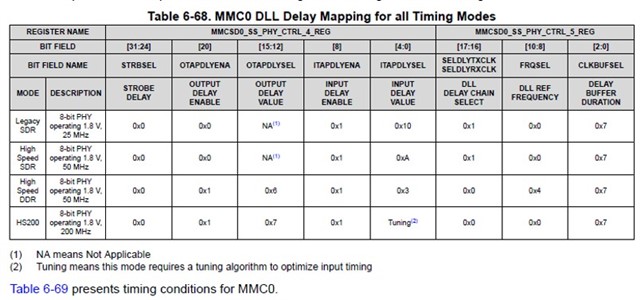

Table 6-68 of the TRM show OTAPDLYSEL is settled to 0x7 that :

What is the corresponding delay value between CLK and others signals?

Thanks for you help.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hello,

I would like to simulate HS200 mode in write phase.

Table 6-68 of the TRM show OTAPDLYSEL is settled to 0x7 that :

What is the corresponding delay value between CLK and others signals?

Thanks for you help.

They are defined in the data sheet table titled "MMC0 Switching Characteristics – HS200 Mode". The conditions for which these values are valid are defined in the datasheet table titled "MMC0 Timing Conditions".

Regards,

Paul

Hello Peaves,

Thanks for your reply.

I've understood, that HS2008 & HS2009 swithching characteristics may vary from 0.99ns to 3.28ns according to OTAPDLYSEL[15..12] values.

The value of 0x7 correspond to which timing value?

Thanks

The OTAPDLYSEL value of 0x7 has a delay variation that can range from 0.99ns to 3.28ns, where this delay range represents what can be expected across process, voltage, and temperature variations of the device. We do not define delay range for any other value of OTAPDLYSEL since this configuration should provide appropriate setup and hold time to the attached device as long as you meet the PCB trace length requirements defined in the Timing Conditions table.

Regards,

Paul