Tool/software:

Hello,

I am trying to use 10G on XFI, for that I want to use a clock frequency of 156.25MHz. The idea is to use the external clock and to use lane 2 of serdes 2 as XFI. If it is also possible to get 156.25MHz from an internal clock that would be good to know.

Here is what I have done so far :

- In k3-j784s4-exp1-exp2-usxgmii.dts, I have changed the speed from 5000 to 10000 :

- &main_cpsw0_port1 {

status = "okay";

phy-mode = "usxgmii";

mac-address = [00 00 00 00 00 00];

phys = <&phy_gmii_sel_cpsw0 1>, <&serdes2_usxgmii_link>;

phy-names = "portmode", "serdes-phy";

fixed-link {

speed = <10000>;

full-duplex;

};

};

- &main_cpsw0_port1 {

- Still in k3-j784s4-exp1-exp2-usxgmii.dts, I checked that serdes2 lane2 was assigned, and as I see it is assigned by default :

- &serdes_ln_ctrl {

idle-states = <J784S4_SERDES0_LANE0_PCIE1_LANE0>, <J784S4_SERDES0_LANE1_PCIE1_LANE1>,

<J784S4_SERDES0_LANE2_IP3_UNUSED>, <J784S4_SERDES0_LANE3_USB>,

<J784S4_SERDES1_LANE0_PCIE0_LANE0>, <J784S4_SERDES1_LANE1_PCIE0_LANE1>,

<J784S4_SERDES1_LANE2_PCIE0_LANE2>, <J784S4_SERDES1_LANE3_PCIE0_LANE3>,

<J784S4_SERDES2_LANE0_IP2_UNUSED>, <J784S4_SERDES2_LANE1_IP2_UNUSED>,

<J784S4_SERDES2_LANE2_QSGMII_LANE1>, <J784S4_SERDES2_LANE3_QSGMII_LANE2>;

};

- &serdes_ln_ctrl {

- In k3-j784s4-evm.dts, I added a node for serdes2 containing the frequency I want to use (156.25MHz) :

- &serdes2_refclk {

clock-frequency = <156250000>;

};*

- &serdes2_refclk {

- In k3-j784s4-main.dtsi, I copied what existed with serdes for serdes2 :

- / {

serdes2_refclk: serdes-refclk {

#clock-cells = <0>;

compatible = "fixed-clock";

};

};

- / {

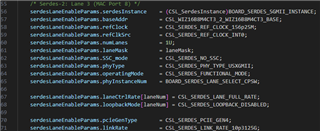

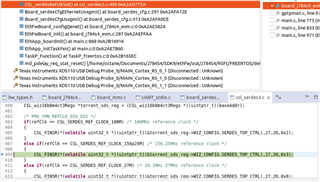

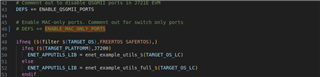

- Still in k3-j784s4-main.dtsi, I replaced &serdes_refclk by &serdes2_refclk and switched the status to "okay" :

-

serdes_wiz2: wiz@5020000 {

compatible = "ti,j784s4-wiz-10g";

#address-cells = <1>;

#size-cells = <1>;

power-domains = <&k3_pds 406 TI_SCI_PD_EXCLUSIVE>;

clocks = <&k3_clks 406 2>, <&k3_clks 406 6>, <&k3_clks 406 5>, <&serdes2_refclk>;

clock-names = "fck", "core_ref_clk", "core_ref1_clk", "ext_ref_clk";

num-lanes = <4>;

#reset-cells = <1>;

#clock-cells = <1>;

ranges = <0x05020000 0x0 0x05020000 0x00010000>;assigned-clocks = <&k3_clks 406 6>;

assigned-clock-parents = <&k3_clks 406 10>;status = "okay";

-

- Still in k3-j784s4-main.dtsiI also understood that I need to use &serdes2_refclk in assigned-clock-parents but I don't understand which PLL to use :

-

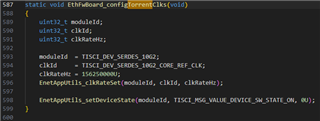

serdes2: serdes@5020000 {

compatible = "ti,j721e-serdes-10g";

reg = <0x05020000 0x00010000>;

reg-names = "torrent_phy";

resets = <&serdes_wiz2 0>;

reset-names = "torrent_reset";

clocks = <&serdes_wiz2 TI_WIZ_PLL0_REFCLK>,

<&serdes_wiz2 TI_WIZ_PHY_EN_REFCLK>;

clock-names = "refclk", "phy_en_refclk";

assigned-clocks = <&serdes_wiz2 TI_WIZ_PLL0_REFCLK>,

<&serdes_wiz2 TI_WIZ_PLL1_REFCLK>,

<&serdes_wiz2 TI_WIZ_REFCLK_DIG>;

assigned-clock-parents = <&k3_clks 406 6>,

<&k3_clks 406 6>,

<&k3_clks 406 6>;

#address-cells = <1>;

#size-cells = <0>;

#clock-cells = <1>;status = "disabled";

};

};

-

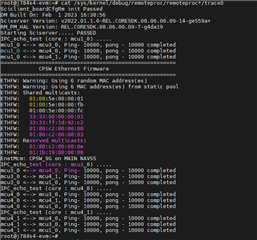

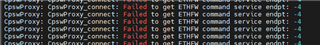

Here are my questions :

- Following the method I just exposed, the remaining task is to assign &serdes2_refclk in the assigned-clock-parents field in red, is it the right way to do ?

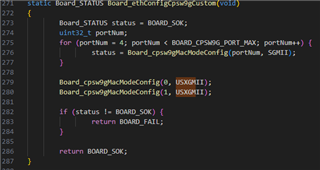

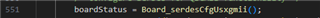

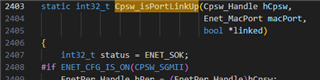

- Do we need to activate the external clock separately ? I imagine it should be activated in the u-boot source code, do you have an idea on its activation process ?

Thank you,

Kind regards,

Wissam