Tool/software:

HI TI,

How to modify dphy_TxByteClkHS_cl_clk and vbus_clk_clk in csitx rtos driver? we used pdk_j721s2_10_00_00_27

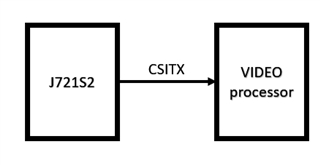

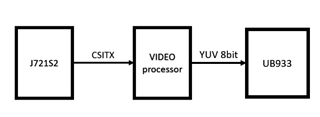

For now,we connected video processor after the J721S2 CSITX output and to Converted CSI to parallel .

The video processor vendor wants to test what happens to the video processor ,if dphy_TxByteClkHS_cl_clk and vbus_clk_clk are changed.

-- Thanks. Best Regards.