Other Parts Discussed in Thread: SYSCONFIG, UNIFLASH

Tool/software:

hi TI experts

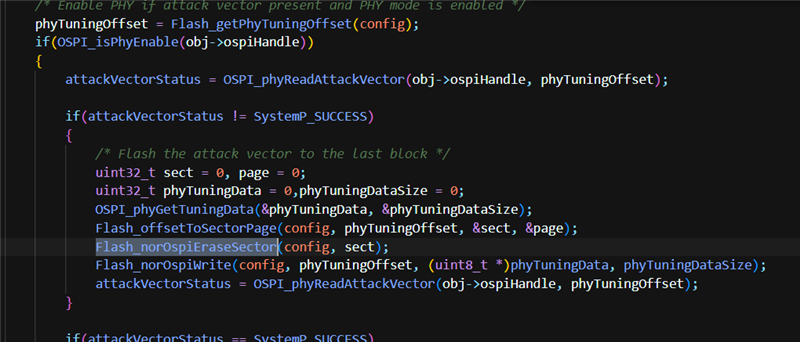

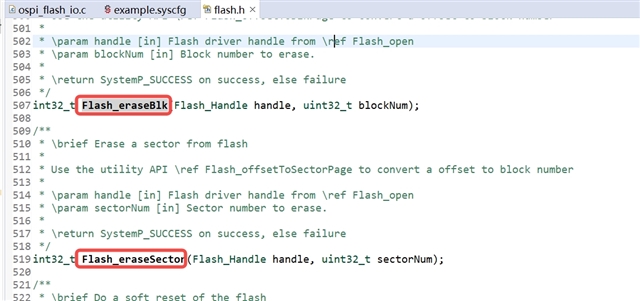

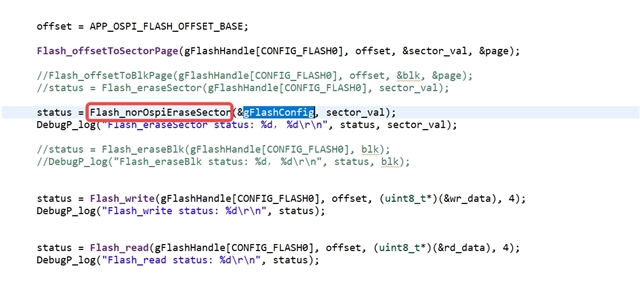

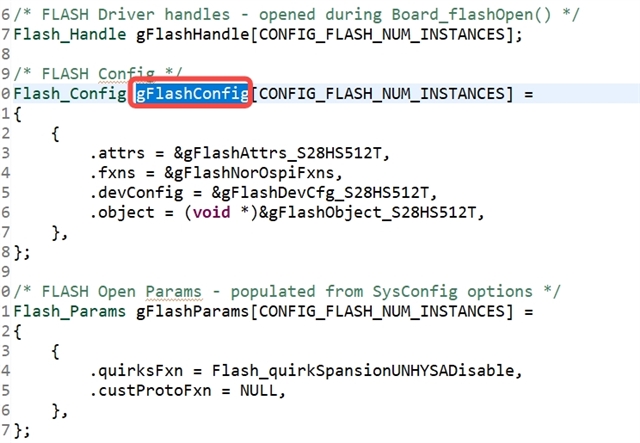

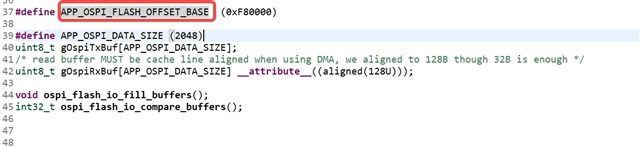

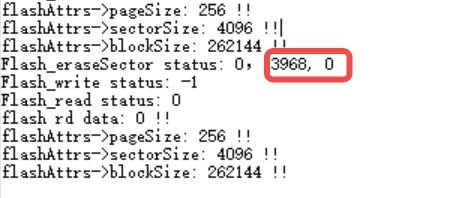

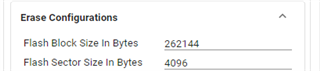

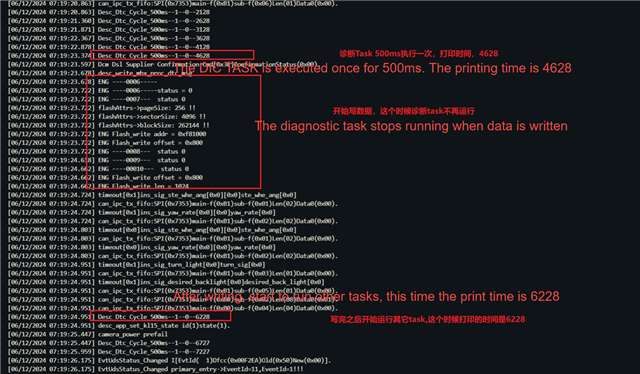

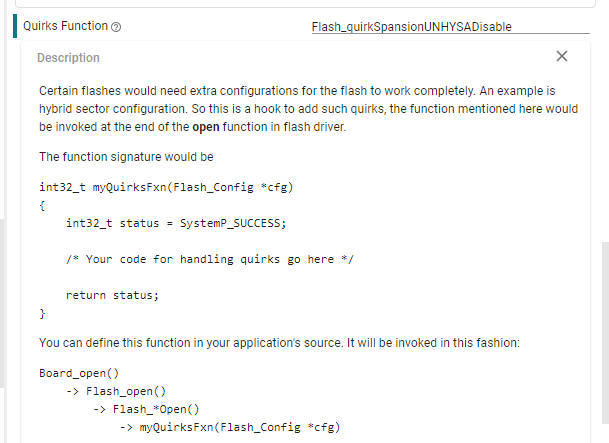

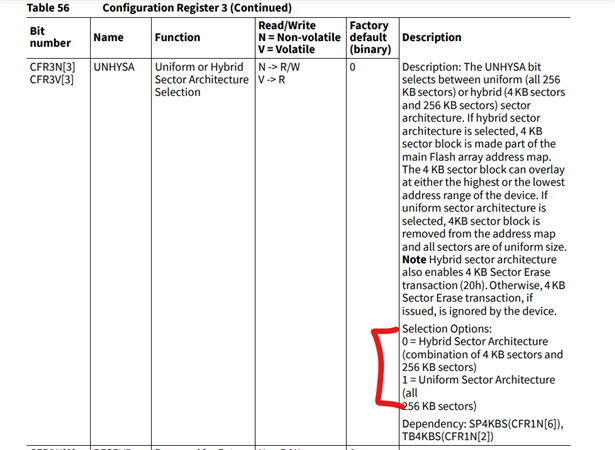

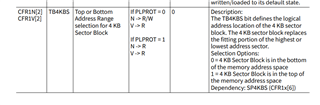

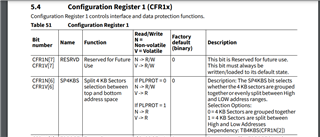

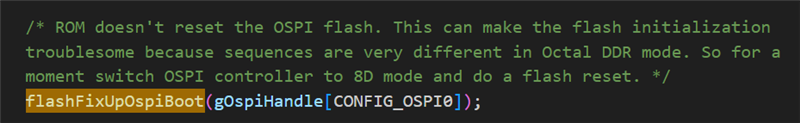

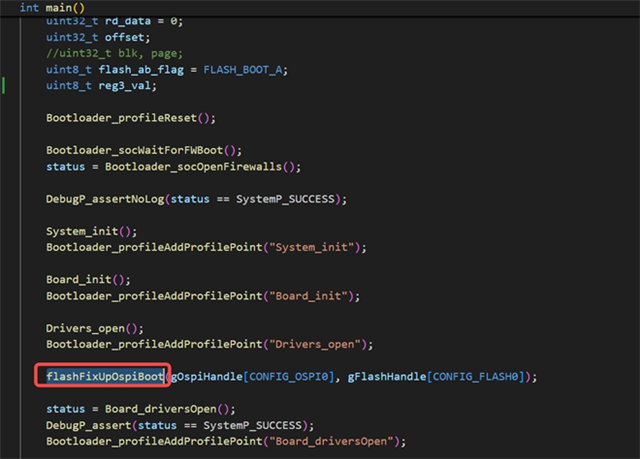

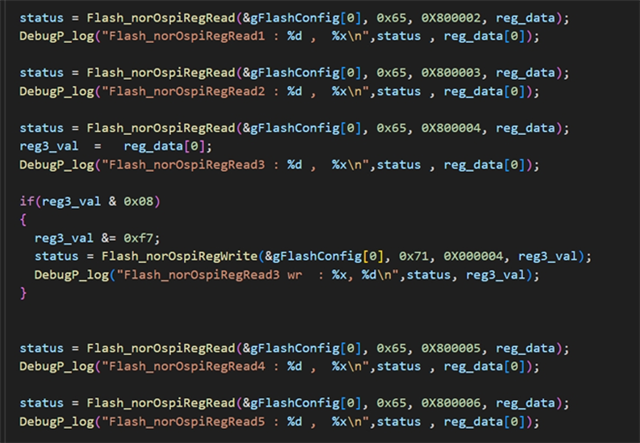

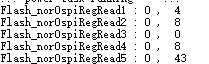

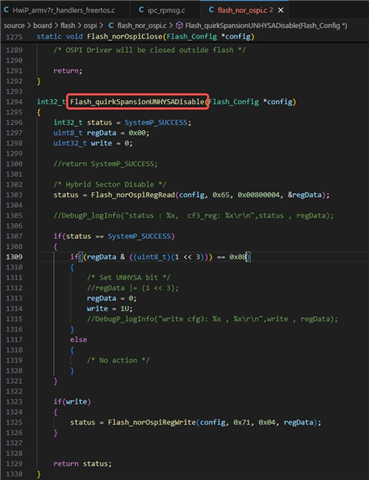

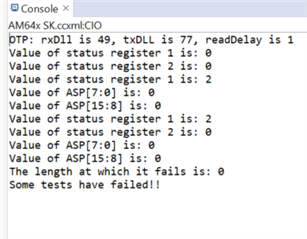

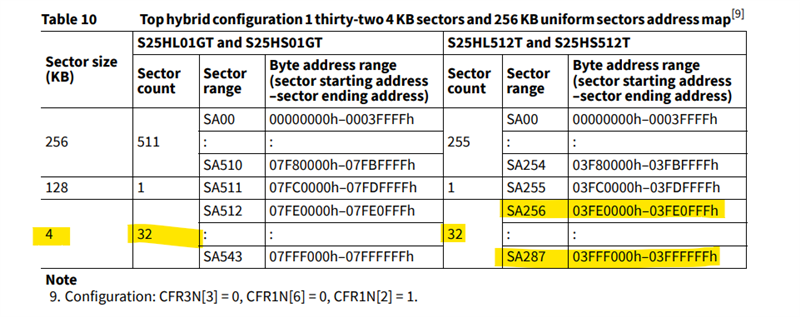

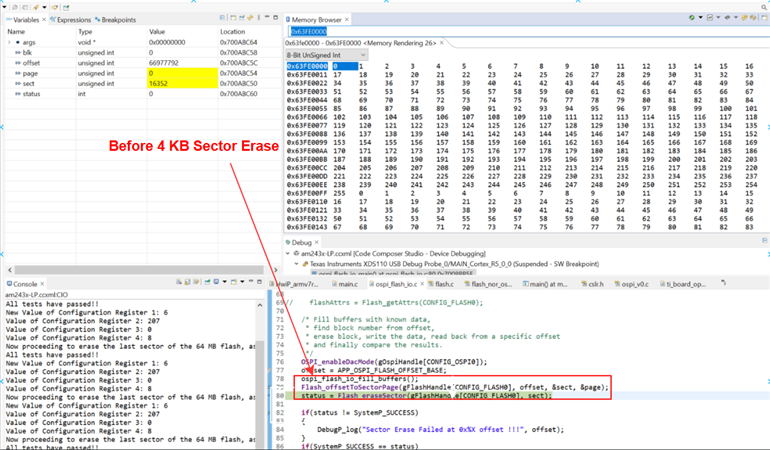

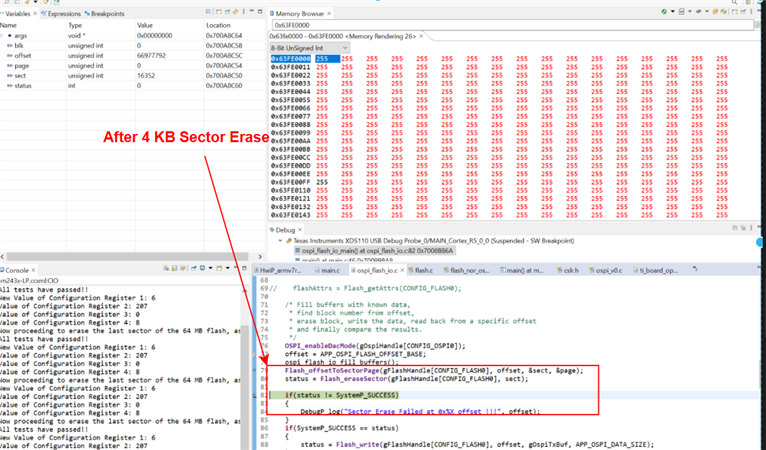

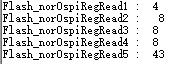

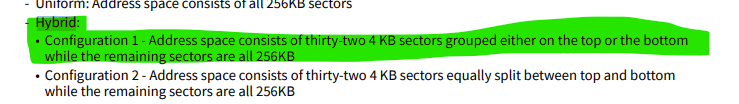

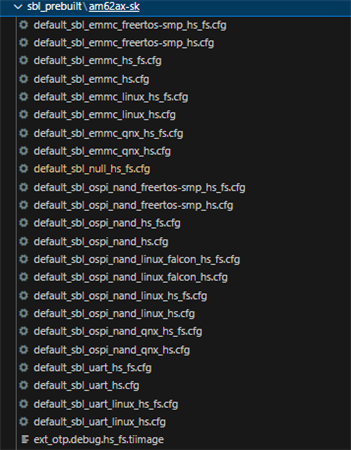

Now we use norflash memory S28HS512T which is accessed through AM62A3 OSPI interface in our customized board, if using " int32_t Flash_eraseBlk(Flash_Handle handle, uint32_t blockNum) " function( erase 256k) , the used flash block can be erased successfully and user data can be wrote to Nor flash device correctly;

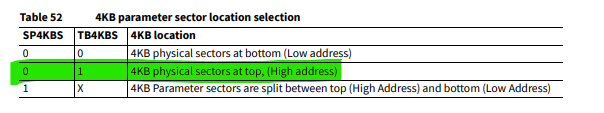

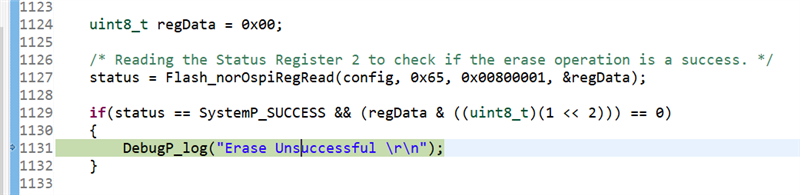

but if use "int32_t Flash_eraseSector(Flash_Handle handle, uint32_t sectorNum) (erase 4K)" function, the erase and write operation will be failed.

in fact, most time we may just modify a few bytes data in one sector; before erasing flash, we can copy one sector data into global buffer , then modify some bytes data according to the data

position offset in the buffer , finally write data stored in buffer to the specified sector area, there is no necessary to erase block area every time ;

so why call the "Flash_eraseSector()" function can`t erase data as expected;