Other Parts Discussed in Thread: DRA821

Tool/software:

Hi team,

I want to know the bottleneck with CPSW5G native Ethernet (following the instructions in https://e2e.ti.com/support/processors-group/processors/f/processors-forum/1264445/faq-how-do-i-bring-brought-up-ethernet-interfaces-for-main-domain-cpswng-in-linux-from-sdk-version-9-0-and-above)

The test environments:

| Board | J721EXCP01EVM www.ti.com/.../J721EXCP01EVM |

| SDK | PROCESSOR-SDK-LINUX-J7200 — Linux SDK for DRA821 Jacinto Processors SDK Version: 10.00.07.03 (https://www.ti.com/tool/PROCESSOR-SDK-J7200) |

| Boot Mode | SD Card |

| Kernel Version | 6.6.32-ti |

Four independent ports in CPSW5G are set to test simultaneously, and the information is as follows:

| eth1 | iperf3 -c 192.168.3.128 -B 192.168.3.127 -p 5201 -t 60 --bind-dev eth1 --logfile 5201.log |

| eth2 | iperf3 -c 192.168.4.128 -B 192.168.4.127 -p 5202 -t 60 --bind-dev eth2 --logfile 5202.log |

| eth3 | iperf3 -c 192.168.5.128 -B 192.168.5.127 -p 5203 -t 60 --bind-dev eth3 --logfile 5203.log |

| eth4 | iperf3 -c 192.168.6.128 -B 192.168.6.127 -p 5204 -t 60 --bind-dev eth4 --logfile 5204.log |

I found that the total throughput does not exceed 2.2Gbps and the CPU usage is around 75% (average of two cores)

LAN1 - - - - - - - - - - - - - - - - - - - - - - - - - [ ID] Interval Transfer Bitrate Retr [ 6] 0.00-60.00 sec 376 MBytes 52.6 Mbits/sec 0 sender [ 6] 0.00-60.04 sec 375 MBytes 52.3 Mbits/sec receiver LAN2 - - - - - - - - - - - - - - - - - - - - - - - - - [ ID] Interval Transfer Bitrate Retr [ 6] 0.00-60.00 sec 3.99 GBytes 571 Mbits/sec 0 sender [ 6] 0.00-60.04 sec 3.99 GBytes 570 Mbits/sec receiver LAN3 - - - - - - - - - - - - - - - - - - - - - - - - - [ ID] Interval Transfer Bitrate Retr [ 6] 0.00-60.00 sec 6.52 GBytes 934 Mbits/sec 0 sender [ 6] 0.00-60.05 sec 6.52 GBytes 933 Mbits/sec receiver LAN4 - - - - - - - - - - - - - - - - - - - - - - - - - [ ID] Interval Transfer Bitrate Retr [ 6] 0.00-60.00 sec 3.98 GBytes 570 Mbits/sec 0 sender [ 6] 0.00-60.05 sec 3.98 GBytes 569 Mbits/sec receiver

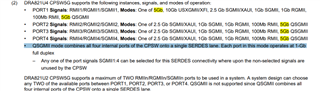

[Question] According to the specification, do the serdes lanes limit the throughput of the native Ethernet?