Tool/software:

Our customer was performing compliance testing for LPDDR4 on their custom board and found an issue with write access. There is almost no skew between DQS and DQ, and DQS and DQ appear to be in phase. On the other hand, there are no issues with read access.

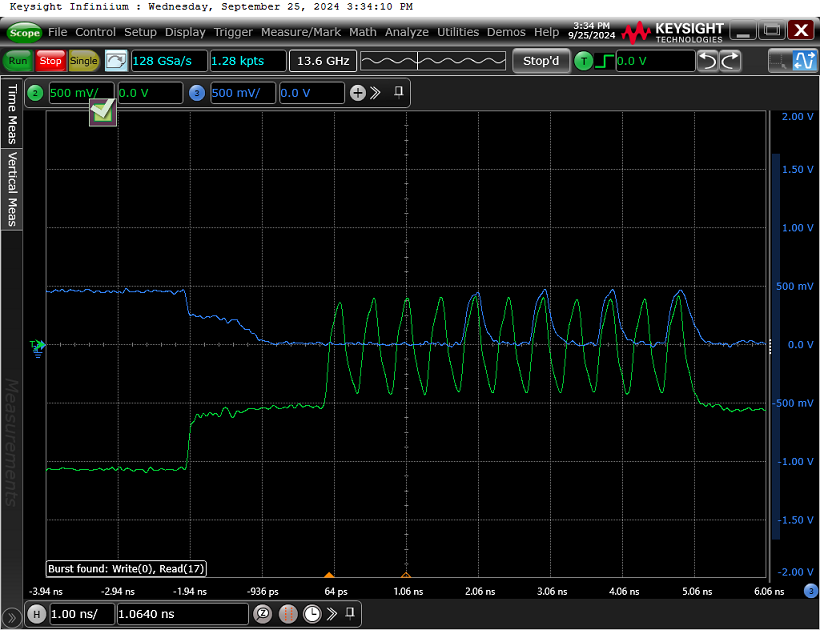

DQS to DQ Skew with write access:

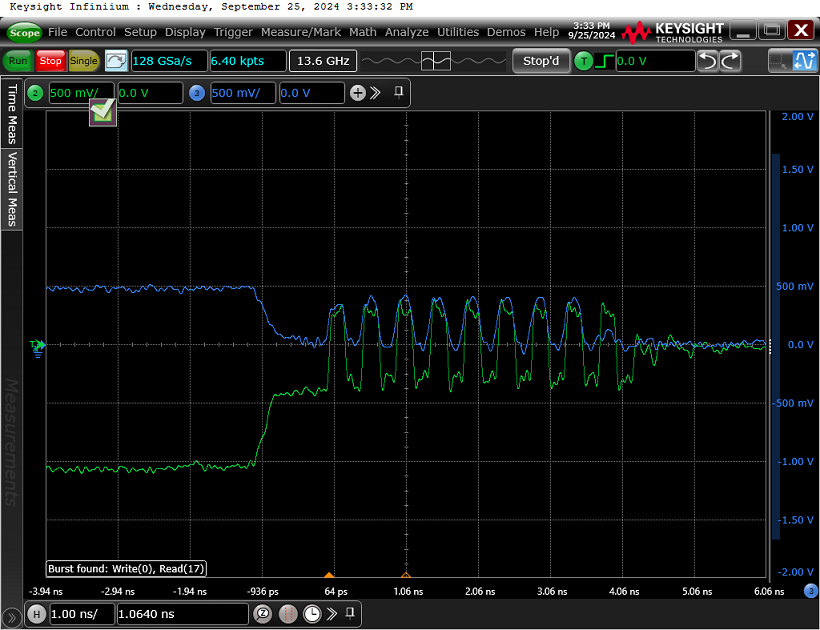

DQS to DQ Skew with read access:

There are no issues with post-simulation in artwork, so there should be no issues with HW design.

Our customer is concerned that Write DQS2DQ Training did not work correctly.

Can the phase between DQS and DQ be manually adjusted? If so, how?

The syscfg file exported from the DDRSS Register Configuration Tool v0.11.0 is attached:

/**

* These arguments were used when this file was generated. They will be automatically applied on subsequent loads

* via the GUI or CLI. Run CLI with '--help' for additional information on how to override these arguments.

* @cliArgs --device "J784S4_TDA4AP_TDA4VP_TDA4AH_TDA4VH_AM69x" --package "ALY" --part "Default" --product "TDA4x_DRA8x_AM67x-AM69x_DDR_Config@0.11.00.0000"

* @versions {"tool":"1.20.0+3587"}

*/

/**

* Import the modules used in this configuration.

*/

const DDRSS = scripting.addModule("/DDRSS");

/**

* Write custom configuration values to the imported modules.

*/

DDRSS.system_cfg_msmc_intlv_size = 8;

DDRSS.system_cfg_soc_number = "AM69x";

DDRSS.lpddr4.$name = "jacinto_lpddr4_DDRSS_LPDDR40";

DDRSS.lpddr4.config_dram1_mr2_rl_FS2 = 36;

DDRSS.lpddr4.config_dram1_mr3_dbi_rd_FS2 = "Disable";

DDRSS.lpddr4.config_dram2_mr3_dbi_wr_FS2 = "Enable";

DDRSS.lpddr4.config_dram3_mr3_dbi_wr_FS2 = "Enable";

DDRSS.lpddr4.config_dram2_tREFIab_ns = 1950;

DDRSS.lpddr4.config_dram2_tRASmax_ns = 17550;

DDRSS.lpddr4.config_dram3_tREFIab_ns = 1950;

DDRSS.lpddr4.config_dram3_tRASmax_ns = 17550;

DDRSS.lpddr4.system_cfg_dram_density = 8;

DDRSS.lpddr4.config_dram_tRFCab_ns = 280;

DDRSS.lpddr4.config_dram_tRFCpb_ns = 140;

DDRSS.lpddr4.config_dram_tXSR_ns = 287.5;

DDRSS.lpddr4.config_dram_mr11_ca_odt_FS2 = "RZQ/5";

DDRSS.lpddr4.config_dram_mr11_dq_odt_FS2 = "RZQ/6";

DDRSS.lpddr4.system_cfg_dram1_density = 8;

DDRSS.lpddr4.config_dram1_tRFCab_ns = 280;

DDRSS.lpddr4.config_dram1_tRFCpb_ns = 140;

DDRSS.lpddr4.config_dram1_tXSR_ns = 287.5;

DDRSS.lpddr4.config_dram1_mr11_ca_odt_FS2 = "RZQ/5";

DDRSS.lpddr4.system_cfg_dram2_density = 8;

DDRSS.lpddr4.config_dram2_tRFCab_ns = 280;

DDRSS.lpddr4.config_dram2_tRFCpb_ns = 140;

DDRSS.lpddr4.config_dram2_tXSR_ns = 287.5;

DDRSS.lpddr4.config_dram2_mr11_ca_odt_FS2 = "RZQ/5";

DDRSS.lpddr4.system_cfg_dram3_density = 8;

DDRSS.lpddr4.config_dram3_tRFCab_ns = 280;

DDRSS.lpddr4.config_dram3_tRFCpb_ns = 140;

DDRSS.lpddr4.config_dram3_tXSR_ns = 287.5;

DDRSS.lpddr4.config_dram3_mr11_ca_odt_FS2 = "RZQ/5";

DDRSS.lpddr4.system_cfg_dram_ranks = 1;

DDRSS.lpddr4.system_cfg_dram1_ranks = 1;

DDRSS.lpddr4.system_cfg_dram2_ranks = 1;

DDRSS.lpddr4.system_cfg_dram3_ranks = 1;

Best regards,

Daisuke