Tool/software:

Hello Nick, Anil, team,

As agreed bringing this discussion to external thread. Summery below of current situation.

The current status:

* we have a hardware timer

* we use an interrupt on the R5

* which triggers a GPIO write

Sadly, we see in real-world applications sometimes a delay of this GPIO trigger in the area of 200-300ns. Which is the typical time we have also seen, that other processes on the AM64 are delayed, probably due to the shared bus.

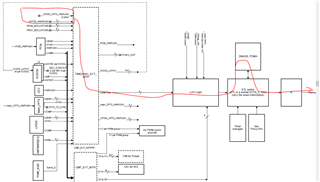

We are looking now to utilize the DMA for this process:

* So we would need a DMA transfer to write to the GPIO register

* This DMA should be triggered by the hardware timer module

* We also have the timer signal routed into the HW_TSxPUSH pin (in case this is of any help)

Can the timer interrupt or the HW_TSxPUSH signal can trigger the DMA to write to the GPIO module?

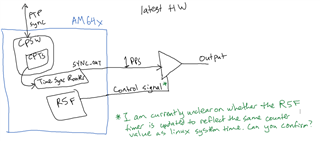

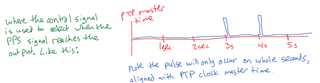

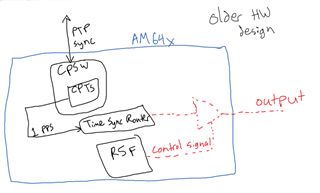

Right now, we already use the CPTS modules:

* CPTS inside GMAC for generating the PTP PPS

* global CPTS to measure synchronization accuracy and comparing PPS signals

* We already route the generated PPS through one of the SYNCx_OUT pins

For our current application:

* As of legacy reasons, our current boards, we connect to the AM64, require a trigger signal on the UART line

* For this purpose, we generate a GPIO falling edge via the R5 interrupt from the reference PPS (AM64 Timer Module)

* If only the main R5 is being active, we see almost no jitter (close to +/-5ns, which is expected due to the 200MHz GPIO clock), as we use only TCM memory for any code or data and disable all other (FreeRTOS) interrupts

* As soon as we have some more background activities (daisy-chained devices, some network traffic), we sometimes see jumps in those delays

We already have added a multiplexer to route the actual PPS signal to the UART line, which resolves the problem on new hardware. We are just looking through, if we could still resolve the issue on existing hardware or at least improve it. For this we thought, we could use the DMA to use the memory bus a bit more efficiently and reduce the latency.

* There are several nice R5 examples of the UDMA usage

* What I'm not sure from the documentation is, how we can trigger the DMA transfer via some sort of PPS signal (we have all required PPS signals running through the TSR, as they are connected to the HWx_TS_PUSH pins)

The FAQ below helps how to trigger DMA based on the GPIO.

Thanks,

Aida