Other Parts Discussed in Thread: AM62P

Tool/software:

Hi TI,

I have a 2 questions related to the Secure Proxy configuration and HSM on the AM62A platform:

-

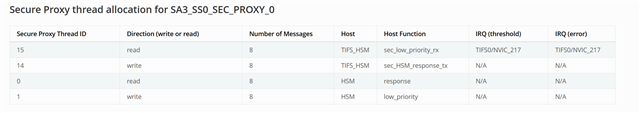

In the Secure Proxy thread allocation table for

SA3_SS0_SEC_PROXY_0, the thread IDs for TIFS_HSM and HSM are listed, but I could not find thread IDs for DM core, MCU core, or A core when communicating with the HSM core.

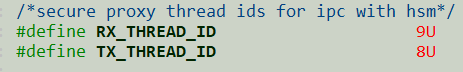

At the same time, the

hsm_ipcdemo definesRX_THREAD_IDas 9 andTX_THREAD_IDas 8.

Accessing sproxy registers with these macro definition results in hard abort. Are these IDs part of another mapping table that is not documented here? If so, could you clarify where I can find this allocation?

-

In the table, TIFS_HSM is listed as a Host for both

sec_low_priority_rxandsec_HSM_response_txthreads. Why are two TIFS_HSM cores acting as Hosts together?

Best regards,

Yang