Tool/software:

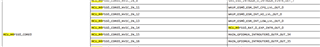

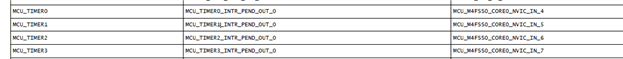

Table 10-11, the interrupt sources on column 2 really confusing users.

In this table, which IRQ number is mapped to system tick ?

What IRQ numbers on the above table are the NVIC IRQ 1-15 mapped to ?

I am expecting that interrupt sources should be meaningful like module (TIMER), event (overflow) combination, not just dump TI internal doc keywords here as user manual

Thanks,

Jim