Tool/software:

Dear TI's experts,

SDK Version:10.01

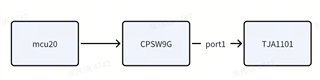

We are currently working on upgrading from sdk8.4 to sdk10.1, but we have found that the modifications made to cpsw9g on sdk8.4 are not working properly on sdk10.1. Can you help me confirm if there are any omissions or inaccuracies in my modifications?

Regards.

From 26afd2ff3d2674c33195e5d6e5ba20b83661a564 Mon Sep 17 00:00:00 2001

From: zhangweizhen <zhangweizhen@mit.cn>

Date: Fri, 28 Feb 2025 15:40:56 +0800

Subject: [PATCH] using cpsw9g on mcu20

Change-Id: I0e6f2df0fa8d5e8521d3a2308bce0055436e54d6

---

.../utils/board/src/j721e/board_j721e_evm.c | 30 +--

.../board/src/j721e_evm/J721E_pinmux_data.c | 2 +

.../j721e_evm/J721E_pinmux_data_gesi_cpsw9g.c | 152 +++++++++++-

.../src/j721e_evm/board_ethernet_config.c | 7 +-

.../packages/ti/drv/enet/enet_cfg.h | 2 +-

.../ti/drv/enet/include/phy/tja1101.h | 104 +++++++++

.../ti/drv/enet/soc/j7x/j721e/enet_soc.c | 2 +-

.../packages/ti/drv/enet/src/phy/enetphy.c | 22 +-

.../packages/ti/drv/enet/src/phy/makefile | 2 +-

.../packages/ti/drv/enet/src/phy/tja1101.c | 221 ++++++++++++++++++

.../ti/drv/enet/src/phy/tja1101_priv.h | 94 ++++++++

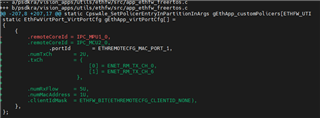

.../utils/ethfw/src/app_ethfw_freertos.c | 105 +--------

.../vision_apps/utils/ethfw/src/concerto.mak | 2 +-

13 files changed, 606 insertions(+), 139 deletions(-)

create mode 100755 psdkra/pdk_jacinto_10_01_00_25/packages/ti/drv/enet/include/phy/tja1101.h

create mode 100755 psdkra/pdk_jacinto_10_01_00_25/packages/ti/drv/enet/src/phy/tja1101.c

create mode 100755 psdkra/pdk_jacinto_10_01_00_25/packages/ti/drv/enet/src/phy/tja1101_priv.h

diff --git a/psdkra/ethfw/utils/board/src/j721e/board_j721e_evm.c b/psdkra/ethfw/utils/board/src/j721e/board_j721e_evm.c

index 8b4c01a2e..8284cd6db 100644

--- a/psdkra/ethfw/utils/board/src/j721e/board_j721e_evm.c

+++ b/psdkra/ethfw/utils/board/src/j721e/board_j721e_evm.c

@@ -200,8 +200,8 @@ extern pinmuxBoardCfg_t gEthFwPinmuxData[];

/* GPIO Driver board specific pin configuration structure */

GPIO_PinConfig gEthFw_gpioPinCfgs[] =

{

- GPIO_DEVICE_CONFIG(0, 61) | GPIO_CFG_OUTPUT,

- GPIO_DEVICE_CONFIG(0, 62) | GPIO_CFG_OUTPUT,

+ GPIO_DEVICE_CONFIG(0, 41) | GPIO_CFG_OUTPUT,

+ GPIO_DEVICE_CONFIG(0, 44) | GPIO_CFG_OUTPUT,

};

/* GPIO Driver callback functions */

@@ -244,6 +244,7 @@ static const Dp83867_Cfg gEnetGesiBoard_dp83867PhyCfg =

/* 4 x RGMII ports in GESI expansion board */

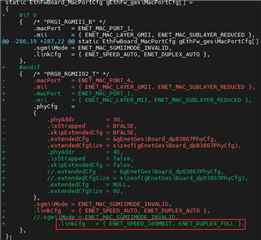

static EthFwBoard_MacPortCfg gEthFw_gesiMacPortCfg[] =

{

+#if 0

{ /* "PRG1_RGMII1_B" */

.macPort = ENET_MAC_PORT_1,

.mii = { ENET_MAC_LAYER_GMII, ENET_MAC_SUBLAYER_REDUCED },

@@ -286,19 +287,22 @@ static EthFwBoard_MacPortCfg gEthFw_gesiMacPortCfg[] =

.sgmiiMode = ENET_MAC_SGMIIMODE_INVALID,

.linkCfg = { ENET_SPEED_AUTO, ENET_DUPLEX_AUTO },

},

+#endif

{ /* "PRG0_RGMII02_T" */

- .macPort = ENET_MAC_PORT_4,

- .mii = { ENET_MAC_LAYER_GMII, ENET_MAC_SUBLAYER_REDUCED },

+ .macPort = ENET_MAC_PORT_1,

+ .mii = { ENET_MAC_LAYER_MII, ENET_MAC_SUBLAYER_REDUCED },

.phyCfg =

{

- .phyAddr = 3U,

- .isStrapped = BFALSE,

- .skipExtendedCfg = BFALSE,

- .extendedCfg = &gEnetGesiBoard_dp83867PhyCfg,

- .extendedCfgSize = sizeof(gEnetGesiBoard_dp83867PhyCfg),

+ .phyAddr = 4U,

+ .isStrapped = false,

+ .skipExtendedCfg = false,

+ //.extendedCfg = &gEnetGesiBoard_dp83867PhyCfg,

+ //.extendedCfgSize = sizeof(gEnetGesiBoard_dp83867PhyCfg),

+ .extendedCfg = NULL,

+ .extendedCfgSize = 0U,

},

- .sgmiiMode = ENET_MAC_SGMIIMODE_INVALID,

- .linkCfg = { ENET_SPEED_AUTO, ENET_DUPLEX_AUTO },

+ //.sgmiiMode = ENET_MAC_SGMIIMODE_INVALID,

+ .linkCfg = { ENET_SPEED_AUTO, ENET_DUPLEX_AUTO },

},

};

@@ -599,7 +603,7 @@ static void EthFwBoard_configPinmux(void)

Board_pinmuxUpdate(gEthFwPinmuxData, BOARD_SOC_DOMAIN_MAIN);

/* Configure pinmux settings for Ethernet ports and MDIO */

- Board_pinmuxUpdate(gJ721E_MainPinmuxDataGesiCpsw9gQsgmii, BOARD_SOC_DOMAIN_MAIN);

+ Board_pinmuxUpdate( gJ721E_MainPinmuxDataGesiCpsw9g, BOARD_SOC_DOMAIN_MAIN);

/* REVISIT - Configure CPSW9G pins for ports on the GESI board */

Board_pinmuxGetCfg(&pinmuxCfg);

@@ -622,7 +626,7 @@ static void EthFwBoard_detectDBs(void)

{

/* Assume expansion boards are present if detection not allowed */

gEthFwBoard.gesiDetected = BTRUE;

- gEthFwBoard.qenetDetected = BTRUE;

+ gEthFwBoard.qenetDetected = BFALSE;

}

}

diff --git a/psdkra/pdk_jacinto_10_01_00_25/packages/ti/board/src/j721e_evm/J721E_pinmux_data.c b/psdkra/pdk_jacinto_10_01_00_25/packages/ti/board/src/j721e_evm/J721E_pinmux_data.c

index 2a71fc5f9..2389bf1cc 100755

--- a/psdkra/pdk_jacinto_10_01_00_25/packages/ti/board/src/j721e_evm/J721E_pinmux_data.c

+++ b/psdkra/pdk_jacinto_10_01_00_25/packages/ti/board/src/j721e_evm/J721E_pinmux_data.c

@@ -460,6 +460,7 @@ static pinmuxPerCfg_t gMcu_fss0_ospi0PinCfg[] =

{PINMUX_END}

};

/*

+#if 0

static pinmuxPerCfg_t gMcu_fss0_ospi1PinCfg[] =

{

// MyMCU_OSPI1 -> MCU_OSPI1_CLK -> F22

@@ -504,6 +505,7 @@ static pinmuxPerCfg_t gMcu_fss0_ospi1PinCfg[] =

},

{PINMUX_END}

};

+#endif

*/

static pinmuxModuleCfg_t gMcu_fss0_ospiPinCfg[] =

{

diff --git a/psdkra/pdk_jacinto_10_01_00_25/packages/ti/board/src/j721e_evm/J721E_pinmux_data_gesi_cpsw9g.c b/psdkra/pdk_jacinto_10_01_00_25/packages/ti/board/src/j721e_evm/J721E_pinmux_data_gesi_cpsw9g.c

index 4c6062269..50a5d46e6 100755

--- a/psdkra/pdk_jacinto_10_01_00_25/packages/ti/board/src/j721e_evm/J721E_pinmux_data_gesi_cpsw9g.c

+++ b/psdkra/pdk_jacinto_10_01_00_25/packages/ti/board/src/j721e_evm/J721E_pinmux_data_gesi_cpsw9g.c

@@ -39,14 +39,15 @@ static pinmuxModuleCfg_t gCpsw9gPinCfg[] =

static pinmuxPerCfg_t gGpio0PinCfg[] =

{

- /* MyGPIO0 -> GPIO0_96 -> T23 */

+ /* MyGPIO1 -> GPIO0_41 -> AD19 */

{

- PIN_RGMII5_RD0, PIN_MODE(7) | \

+ PIN_PRG1_MDIO0_MDIO, PIN_MODE(7) | \

((PIN_PULL_DISABLE | PIN_INPUT_ENABLE) & (~PIN_PULL_DIRECTION))

},

- /* MyGPIO0 -> GPIO0_104 -> W26 */

+

+ /* MyGPIO1 -> GPIO0_44 -> AE28 */

{

- PIN_RGMII6_RXC, PIN_MODE(7) | \

+ PIN_PRG0_PRU0_GPO1, PIN_MODE(7) | \

((PIN_PULL_DISABLE | PIN_INPUT_ENABLE) & (~PIN_PULL_DIRECTION))

},

{PINMUX_END}

@@ -154,6 +155,125 @@ static pinmuxPerCfg_t gRgmii3PinCfg[] =

{PINMUX_END}

};

+static pinmuxPerCfg_t gRmii1PinCfg[] =

+{

+ /* MyRMII1 -> RMII1_CRS_DV -> AF22 */

+ {

+ PIN_PRG1_PRU0_GPO2, PIN_MODE(5) | \

+ ((PIN_PULL_DISABLE | PIN_INPUT_ENABLE) & (~PIN_PULL_DIRECTION))

+ },

+ /* MyRMII1 -> RMII1_RXD0 -> AC23 */

+ {

+ PIN_PRG1_PRU0_GPO0, PIN_MODE(5) | \

+ ((PIN_PULL_DISABLE | PIN_INPUT_ENABLE) & (~PIN_PULL_DIRECTION))

+ },

+ /* MyRMII1 -> RMII1_RXD1 -> AG22 */

+ {

+ PIN_PRG1_PRU0_GPO1, PIN_MODE(5) | \

+ ((PIN_PULL_DISABLE | PIN_INPUT_ENABLE) & (~PIN_PULL_DIRECTION))

+ },

+ /* MyRMII1 -> RMII1_RX_ER -> AJ23 */

+ {

+ PIN_PRG1_PRU0_GPO3, PIN_MODE(5) | \

+ ((PIN_PULL_DISABLE | PIN_INPUT_ENABLE) & (~PIN_PULL_DIRECTION))

+ },

+ /* MyRMII1 -> RMII1_TXD0 -> AH23 */

+ {

+ PIN_PRG1_PRU0_GPO4, PIN_MODE(5) | \

+ ((PIN_PULL_DISABLE) & (~PIN_PULL_DIRECTION & ~PIN_INPUT_ENABLE))

+ },

+ /* MyRMII1 -> RMII1_TXD1 -> AD22 */

+ {

+ PIN_PRG1_PRU0_GPO6, PIN_MODE(5) | \

+ ((PIN_PULL_DISABLE) & (~PIN_PULL_DIRECTION & ~PIN_INPUT_ENABLE))

+ },

+ /* MyRMII1 -> RMII1_TX_EN -> AD20 */

+ {

+ PIN_PRG1_PRU0_GPO5, PIN_MODE(5) | \

+ ((PIN_PULL_DISABLE) & (~PIN_PULL_DIRECTION & ~PIN_INPUT_ENABLE))

+ },

+

+ {

+ PIN_PRG1_MDIO0_MDC, PIN_MODE(5) | \

+ ((PIN_PULL_DISABLE | PIN_INPUT_ENABLE) & (~PIN_PULL_DIRECTION))

+ },

+

+ {PINMUX_END}

+};

+

+static pinmuxPerCfg_t gRmii4PinCfg[] =

+{

+ /* MyRMII1 -> RMII4_CRS_DV -> AD27 */

+ {

+ PIN_PRG0_PRU1_GPO2, PIN_MODE(5) | \

+ ((PIN_PULL_DISABLE | PIN_INPUT_ENABLE) & (~PIN_PULL_DIRECTION))

+ },

+ /* MyRMII1 -> RMII4_RXD0 -> AE29 */

+ {

+ PIN_PRG0_PRU1_GPO0, PIN_MODE(5) | \

+ ((PIN_PULL_DISABLE | PIN_INPUT_ENABLE) & (~PIN_PULL_DIRECTION))

+ },

+ /* MyRMII1 -> RMII4_RXD1 -> AD28 */

+ {

+ PIN_PRG0_PRU1_GPO1, PIN_MODE(5) | \

+ ((PIN_PULL_DISABLE | PIN_INPUT_ENABLE) & (~PIN_PULL_DIRECTION))

+ },

+ /* MyRMII1 -> RMII4_RX_ER -> AC25 */

+ {

+ PIN_PRG0_PRU1_GPO3, PIN_MODE(5) | \

+ ((PIN_PULL_DISABLE | PIN_INPUT_ENABLE) & (~PIN_PULL_DIRECTION))

+ },

+ /* MyRMII1 -> RMII4_TXD0 -> AC26 */

+ {

+ PIN_PRG0_PRU1_GPO6, PIN_MODE(5) | \

+ ((PIN_PULL_DISABLE) & (~PIN_PULL_DIRECTION & ~PIN_INPUT_ENABLE))

+ },

+ /* MyRMII1 -> RMII4_TXD1 -> AD29 */

+ {

+ PIN_PRG0_PRU1_GPO4, PIN_MODE(5) | \

+ ((PIN_PULL_DISABLE) & (~PIN_PULL_DIRECTION & ~PIN_INPUT_ENABLE))

+ },

+ /* MyRMII1 -> RMII4_TX_EN -> AG26 */

+ {

+ PIN_PRG0_PRU1_GPO11, PIN_MODE(5) | \

+ ((PIN_PULL_DISABLE) & (~PIN_PULL_DIRECTION & ~PIN_INPUT_ENABLE))

+ },

+

+

+ {

+ PIN_PRG1_MDIO0_MDC, PIN_MODE(5) | \

+ ((PIN_PULL_DISABLE | PIN_INPUT_ENABLE) & (~PIN_PULL_DIRECTION))

+ },

+

+

+ /* MyRGMII4 -> RGMII4_TD1 -> AF27 */

+ /*{

+ PIN_PRG0_PRU1_GPO12, PIN_MODE(5) | \

+ ((PIN_PULL_DISABLE) & (~PIN_PULL_DIRECTION & ~PIN_INPUT_ENABLE))

+ },*/

+ /* MyRGMII4 -> RGMII4_TD2 -> AF26 */

+ /*{

+ PIN_PRG0_PRU1_GPO13, PIN_MODE(5) | \

+ ((PIN_PULL_DISABLE) & (~PIN_PULL_DIRECTION & ~PIN_INPUT_ENABLE))

+ },*/

+ /* MyRGMII4 -> RGMII4_TD3 -> AE25 */

+ /*{

+ PIN_PRG0_PRU1_GPO14, PIN_MODE(5) | \

+ ((PIN_PULL_DISABLE) & (~PIN_PULL_DIRECTION & ~PIN_INPUT_ENABLE))

+ },*/

+ /* MyRGMII4 -> RGMII4_TXC -> AG29 */

+ /*{

+ PIN_PRG0_PRU1_GPO16, PIN_MODE(5) | \

+ ((PIN_PULL_DISABLE | PIN_INPUT_ENABLE) & (~PIN_PULL_DIRECTION))

+ },*/

+ /* MyRGMII4 -> RGMII4_TX_CTL -> AF29 */

+ /*{

+ PIN_PRG0_PRU1_GPO15, PIN_MODE(5) | \

+ ((PIN_PULL_DISABLE | PIN_INPUT_ENABLE) & (~PIN_PULL_DIRECTION))

+ },*/

+ {PINMUX_END}

+};

+

static pinmuxPerCfg_t gRgmii4PinCfg[] =

{

/* MyRGMII4 -> RGMII4_RD0 -> AE29 */

@@ -481,12 +601,21 @@ static pinmuxPerCfg_t gRgmii8PinCfg[] =

{PINMUX_END}

};

-static pinmuxModuleCfg_t gRgmiiPinCfg[] =

+/*static pinmuxModuleCfg_t gRgmiiPinCfg[] =

{

- {3, 1, gRgmii3PinCfg},

- {4, 1, gRgmii4PinCfg},

- {1, 1, gRgmii1PinCfg},

- {2, 1, gRgmii2PinCfg},

+ {3, TRUE, gRgmii3PinCfg},

+ {4, TRUE, gRgmii4PinCfg},

+ {1, TRUE, gRgmii1PinCfg},

+ {2, TRUE, gRgmii2PinCfg},

+ {PINMUX_END}

+};*/

+

+static pinmuxModuleCfg_t g_MtRgmiiPinCfg[] =

+{

+ {3, 0, gRgmii3PinCfg},

+ {4, 0, gRmii4PinCfg},

+ {1, 1, gRmii1PinCfg},

+ {2, 0, gRgmii2PinCfg},

{PINMUX_END}

};

@@ -573,8 +702,9 @@ pinmuxBoardCfg_t gJ721E_MainPinmuxDataGesiCpsw9g[] =

{0, gCpsw9gPinCfg},

{1, gGpioPinCfg},

{2, gMdioPinCfg},

- {3, gRgmiiPinCfg},

- {4, gRmiiPinCfg},

+ /*{3, gRgmiiPinCfg},*/

+ {3, g_MtRgmiiPinCfg},

+ /*{4, gRmiiPinCfg},*/

{PINMUX_END}

};

diff --git a/psdkra/pdk_jacinto_10_01_00_25/packages/ti/board/src/j721e_evm/board_ethernet_config.c b/psdkra/pdk_jacinto_10_01_00_25/packages/ti/board/src/j721e_evm/board_ethernet_config.c

index 5d513ea49..eedd0a767 100755

--- a/psdkra/pdk_jacinto_10_01_00_25/packages/ti/board/src/j721e_evm/board_ethernet_config.c

+++ b/psdkra/pdk_jacinto_10_01_00_25/packages/ti/board/src/j721e_evm/board_ethernet_config.c

@@ -745,12 +745,9 @@ Board_STATUS Board_ethConfigCpsw9g(void)

/* Configures the CPSW9G RGMII ports */

for(portNum = 0; portNum < BOARD_CPSW9G_PORT_MAX; portNum++)

{

- if ( (0U == portNum) ||

- (2U == portNum) ||

- (3U == portNum) ||

- (7U == portNum) )

+ if ( 0U == portNum )

{

- status = Board_cpsw9gEthConfig(portNum, RGMII);

+ status = Board_cpsw9gEthConfig(portNum, RMII);

}

else

{

diff --git a/psdkra/pdk_jacinto_10_01_00_25/packages/ti/drv/enet/enet_cfg.h b/psdkra/pdk_jacinto_10_01_00_25/packages/ti/drv/enet/enet_cfg.h

index e007b849e..730e14ead 100644

--- a/psdkra/pdk_jacinto_10_01_00_25/packages/ti/drv/enet/enet_cfg.h

+++ b/psdkra/pdk_jacinto_10_01_00_25/packages/ti/drv/enet/enet_cfg.h

@@ -89,7 +89,7 @@ extern "C" {

/* --------------------------------------------------------------------------*/

/*! \brief CPSW Q/SGMII support (requires #ENET_CFG_CPSW_MACPORT_SGMII). */

-#define ENET_CFG_CPSW_SGMII (ENET_ON)

+//#define ENET_CFG_CPSW_SGMII (ENET_ON)

/*! \brief CPSW interVLAN support support (requires #ENET_CFG_CPSW_MACPORT_INTERVLAN). */

#define ENET_CFG_CPSW_INTERVLAN (ENET_ON)

diff --git a/psdkra/pdk_jacinto_10_01_00_25/packages/ti/drv/enet/include/phy/tja1101.h b/psdkra/pdk_jacinto_10_01_00_25/packages/ti/drv/enet/include/phy/tja1101.h

new file mode 100755

index 000000000..44aa8273b

--- /dev/null

+++ b/psdkra/pdk_jacinto_10_01_00_25/packages/ti/drv/enet/include/phy/tja1101.h

@@ -0,0 +1,104 @@

+/*

+ * Copyright (c) Texas Instruments Incorporated 2020

+ *

+ * Redistribution and use in source and binary forms, with or without

+ * modification, are permitted provided that the following conditions

+ * are met:

+ *

+ * Redistributions of source code must retain the above copyright

+ * notice, this list of conditions and the following disclaimer.

+ *

+ * Redistributions in binary form must reproduce the above copyright

+ * notice, this list of conditions and the following disclaimer in the

+ * documentation and/or other materials provided with the

+ * distribution.

+ *

+ * Neither the name of Texas Instruments Incorporated nor the names of

+ * its contributors may be used to endorse or promote products derived

+ * from this software without specific prior written permission.

+ *

+ * THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS

+ * "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT

+ * LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR

+ * A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT

+ * OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL,

+ * SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT

+ * LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE,

+ * DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY

+ * THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT

+ * (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE

+ * OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

+ */

+

+/*!

+ * \file tja1101.h

+ *

+ * \brief This file contains the type definitions and helper macros for the

+ * TJA1101 Ethernet PHY.

+ */

+

+/*!

+ * \ingroup DRV_ENETPHY

+ * \defgroup ENETPHY_TJA1101 TI TJA1101 PHY

+ *

+ * TI TJA1101 RMII Ethernet PHY.

+ *

+ * @{

+ */

+

+#ifndef TJA1101_H_

+#define TJA1101_H_

+

+/* ========================================================================== */

+/* Include Files */

+/* ========================================================================== */

+

+#include <stdint.h>

+

+#ifdef __cplusplus

+extern "C" {

+#endif

+

+/* ========================================================================== */

+/* Macros */

+/* ========================================================================== */

+

+/* None */

+

+/* ========================================================================== */

+/* Structures and Enums */

+/* ========================================================================== */

+

+/* None */

+

+/* ========================================================================== */

+/* Global Variables Declarations */

+/* ========================================================================== */

+

+/* None */

+

+/* ========================================================================== */

+/* Function Declarations */

+/* ========================================================================== */

+

+/* None */

+

+/* ========================================================================== */

+/* Deprecated Function Declarations */

+/* ========================================================================== */

+

+/* None */

+

+/* ========================================================================== */

+/* Static Function Definitions */

+/* ========================================================================== */

+

+/* None */

+

+#ifdef __cplusplus

+}

+#endif

+

+#endif /* TJA1101_H_ */

+

+/* @} */

diff --git a/psdkra/pdk_jacinto_10_01_00_25/packages/ti/drv/enet/soc/j7x/j721e/enet_soc.c b/psdkra/pdk_jacinto_10_01_00_25/packages/ti/drv/enet/soc/j7x/j721e/enet_soc.c

index 67d934d35..771a0d1fc 100644

--- a/psdkra/pdk_jacinto_10_01_00_25/packages/ti/drv/enet/soc/j7x/j721e/enet_soc.c

+++ b/psdkra/pdk_jacinto_10_01_00_25/packages/ti/drv/enet/soc/j7x/j721e/enet_soc.c

@@ -1184,7 +1184,7 @@ int32_t EnetSoc_getMacPortMii(Enet_Type enetType,

{

EnetMac_LayerType *enetLayer = &mii->layerType;

EnetMac_SublayerType *enetSublayer = &mii->sublayerType;

- uint32_t modeSel = CPSW_ENET_CTRL_MODE_RGMII;

+ uint32_t modeSel = CPSW_ENET_CTRL_MODE_RMII;

int32_t status = ENET_EFAIL;

switch (enetType)

diff --git a/psdkra/pdk_jacinto_10_01_00_25/packages/ti/drv/enet/src/phy/enetphy.c b/psdkra/pdk_jacinto_10_01_00_25/packages/ti/drv/enet/src/phy/enetphy.c

index 6a6baddad..c8c2520a6 100644

--- a/psdkra/pdk_jacinto_10_01_00_25/packages/ti/drv/enet/src/phy/enetphy.c

+++ b/psdkra/pdk_jacinto_10_01_00_25/packages/ti/drv/enet/src/phy/enetphy.c

@@ -188,6 +188,7 @@ extern EnetPhy_Drv gEnetPhyDrvGeneric;

extern EnetPhy_Drv gEnetPhyDrvDp83822;

extern EnetPhy_Drv gEnetPhyDrvDp83867;

extern EnetPhy_Drv gEnetPhyDrvVsc8514;

+extern EnetPhy_Drv gEnetPhyDrvTja1101;

/*! \brief All the registered PHY specific drivers. */

static EnetPhyDrv_Handle gEnetPhyDrvs[] =

@@ -195,6 +196,7 @@ static EnetPhyDrv_Handle gEnetPhyDrvs[] =

&gEnetPhyDrvVsc8514, /* VSC8514 */

&gEnetPhyDrvDp83822, /* DP83822 */

&gEnetPhyDrvDp83867, /* DP83867 */

+ &gEnetPhyDrvTja1101, /*TJA1101 */

&gEnetPhyDrvGeneric, /* Generic PHY - must be last */

};

@@ -964,9 +966,18 @@ static void EnetPhy_initState(EnetPhy_Handle hPhy)

{

EnetPhy_State *state = &hPhy->state;

- state->speed = ENETPHY_SPEED_10MBIT;

- state->duplexity = ENETPHY_DUPLEX_HALF;

- state->phyLinkCaps = 0U;

+ if(hPhy->addr == 4)

+ {

+ state->speed = ENETPHY_SPEED_100MBIT;

+ state->duplexity = ENETPHY_DUPLEX_FULL;

+ state->phyLinkCaps = 0U;

+ }

+ else

+ {

+ state->speed = ENETPHY_SPEED_10MBIT;

+ state->duplexity = ENETPHY_DUPLEX_HALF;

+ state->phyLinkCaps = 0U;

+ }

if (hPhy->phyCfg.isStrapped)

{

@@ -1125,7 +1136,10 @@ static void EnetPhy_enableState(EnetPhy_Handle hPhy)

ENETTRACE_DBG("PHY %u: req caps: %s",

hPhy->addr, EnetPhy_getCapsString(hPhy->reqLinkCaps));

- status = EnetPhy_getLocalCaps(hPhy, &state->phyLinkCaps);

+ if(hPhy->addr == 4)

+ state->phyLinkCaps = ENETPHY_LINK_CAP_FD100;

+ else

+ status = EnetPhy_getLocalCaps(hPhy, &state->phyLinkCaps);

}

if (status == ENETPHY_SOK)

diff --git a/psdkra/pdk_jacinto_10_01_00_25/packages/ti/drv/enet/src/phy/makefile b/psdkra/pdk_jacinto_10_01_00_25/packages/ti/drv/enet/src/phy/makefile

index f4c3b7233..f6715cfb2 100644

--- a/psdkra/pdk_jacinto_10_01_00_25/packages/ti/drv/enet/src/phy/makefile

+++ b/psdkra/pdk_jacinto_10_01_00_25/packages/ti/drv/enet/src/phy/makefile

@@ -19,7 +19,7 @@ INCLUDE_INTERNAL_INTERFACES =

# Common source files and CFLAGS across all platforms and cores

SRCS_COMMON += enetphy.c generic_phy.c

-SRCS_COMMON += dp83867.c dp83822.c vsc8514.c

+SRCS_COMMON += dp83867.c dp83822.c vsc8514.c tja1101.c

PACKAGE_SRCS_COMMON = $(SRCDIR)

CFLAGS_LOCAL_COMMON = $(PDK_CFLAGS) $(ENET_CFLAGS)

diff --git a/psdkra/pdk_jacinto_10_01_00_25/packages/ti/drv/enet/src/phy/tja1101.c b/psdkra/pdk_jacinto_10_01_00_25/packages/ti/drv/enet/src/phy/tja1101.c

new file mode 100755

index 000000000..45353f9b1

--- /dev/null

+++ b/psdkra/pdk_jacinto_10_01_00_25/packages/ti/drv/enet/src/phy/tja1101.c

@@ -0,0 +1,221 @@

+/*

+ * Copyright (c) Texas Instruments Incorporated 2020

+ *

+ * Redistribution and use in source and binary forms, with or without

+ * modification, are permitted provided that the following conditions

+ * are met:

+ *

+ * Redistributions of source code must retain the above copyright

+ * notice, this list of conditions and the following disclaimer.

+ *

+ * Redistributions in binary form must reproduce the above copyright

+ * notice, this list of conditions and the following disclaimer in the

+ * documentation and/or other materials provided with the

+ * distribution.

+ *

+ * Neither the name of Texas Instruments Incorporated nor the names of

+ * its contributors may be used to endorse or promote products derived

+ * from this software without specific prior written permission.

+ *

+ * THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS

+ * "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT

+ * LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR

+ * A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT

+ * OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL,

+ * SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT

+ * LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE,

+ * DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY

+ * THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT

+ * (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE

+ * OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

+ */

+

+/*!

+ * \file tja1101.c

+ *

+ * \brief This file contains the implementation of the TJA1101 PHY.

+ */

+

+/* ========================================================================== */

+/* Include Files */

+/* ========================================================================== */

+

+#include <stdint.h>

+#include <ti/drv/enet/include/core/enet_utils.h>

+#include <ti/drv/enet/priv/core/enet_trace_priv.h>

+#include <ti/drv/enet/include/phy/enetphy.h>

+#include <ti/drv/enet/include/phy/tja1101.h>

+#include "enetphy_priv.h"

+#include "generic_phy.h"

+#include "tja1101_priv.h"

+

+//extern void EthFwBoard_configGesi(void);

+bool static isResetDone = false;

+/* ========================================================================== */

+/* Macros & Typedefs */

+/* ========================================================================== */

+

+#define TJA1101_OUI (0x6037U)

+#define TJA1101_MODEL (0x10U)

+#define TJA1101_REV (0x2U)

+

+/* ========================================================================== */

+/* Structure Declarations */

+/* ========================================================================== */

+

+static bool Tja1101_isPhyDevSupported(EnetPhy_Handle hPhy,

+ const EnetPhy_Version *version);

+

+static bool Tja1101_isMacModeSupported(EnetPhy_Handle hPhy,

+ EnetPhy_Mii mii);

+

+static int32_t Tja1101_config(EnetPhy_Handle hPhy,

+ const EnetPhy_Cfg *cfg,

+ EnetPhy_Mii mii);

+

+void Tja1101_reset(EnetPhy_Handle hPhy);

+

+bool Tja1101_isResetComplete(EnetPhy_Handle hPhy);

+

+static void Tja1101_printRegs(EnetPhy_Handle hPhy);

+

+/* ========================================================================== */

+/* Function Declarations */

+/* ========================================================================== */

+

+/* None */

+

+/* ========================================================================== */

+/* Global Variables */

+/* ========================================================================== */

+

+EnetPhy_Drv gEnetPhyDrvTja1101 =

+{

+ .name = "tja1101",

+ .isPhyDevSupported = Tja1101_isPhyDevSupported,

+ .isMacModeSupported = Tja1101_isMacModeSupported,

+ .config = Tja1101_config,

+ .reset = Tja1101_reset,

+ .isResetComplete = Tja1101_isResetComplete,

+ .readExtReg = GenericPhy_readExtReg,

+ .writeExtReg = GenericPhy_writeExtReg,

+ .printRegs = Tja1101_printRegs,

+};

+

+/* ========================================================================== */

+/* Function Definitions */

+/* ========================================================================== */

+

+static bool Tja1101_isPhyDevSupported(EnetPhy_Handle hPhy,

+ const EnetPhy_Version *version)

+{

+ bool supported = false;

+

+ if ((version->oui == TJA1101_OUI) &&

+ (version->model == TJA1101_MODEL) &&

+ (version->revision == TJA1101_REV))

+ {

+ supported = true;

+ }

+

+ return supported;

+}

+

+static bool Tja1101_isMacModeSupported(EnetPhy_Handle hPhy,

+ EnetPhy_Mii mii)

+{

+ bool supported;

+

+ switch (mii)

+ {

+ case ENETPHY_MAC_MII_RMII:

+ supported = true;

+ break;

+

+ /* This driver doesn't support MII and RGMII interfaces,

+ * but the TJA1101 PHY does support them */

+ case ENETPHY_MAC_MII_MII:

+ case ENETPHY_MAC_MII_RGMII:

+ default:

+ supported = false;

+ break;

+ }

+

+ return supported;

+}

+

+static int32_t Tja1101_config(EnetPhy_Handle hPhy,

+ const EnetPhy_Cfg *cfg,

+ EnetPhy_Mii mii)

+{

+ //uint16_t i;

+ int32_t status = ENETPHY_SOK;

+ uint16_t val;

+

+#if 1

+ if(hPhy->addr == 4)

+ {

+ /* enable the register RW */

+ EnetPhy_writeReg(hPhy, 17, 0x9804);

+

+ /* RMII mode enabled (50 MHz input on REF_CLK) */

+ EnetPhy_writeReg(hPhy, 18, 0xDE05);

+

+ /* 50 MHz input at REF_CLK; RMII mode only; no XTAL; no clock at CLK_IN_OUT */

+ EnetPhy_readReg(hPhy, 27, &val);

+ val &= ~(3 << 12);

+ EnetPhy_writeReg(hPhy, 27, val);

+ }

+#else

+ // not do anything

+#endif

+ /*if( hPhy->addr == 4 )

+ {

+ for(i = 0; i <= 28; i++)

+ {

+ EnetPhy_readReg(hPhy, i, &val);

+ [>ENETTRACE_DBG("PHY %u: register%u = 0x%04x\n", hPhy->addr, i, val);<]

+ EnetUtils_printf("PHY %u: register%u = 0x%04x\n", hPhy->addr, i, val);

+ }

+ }*/

+

+ return status;

+}

+

+void Tja1101_reset(EnetPhy_Handle hPhy)

+{

+ ENETTRACE_DBG("PHY %u: reset\n", hPhy->addr);

+ //EthFwBoard_configGesi();

+ EnetPhy_writeReg(hPhy, 17, 0x9804);

+ /* Reset the PHY */

+ EnetPhy_rmwReg(hPhy, PHY_BMCR, BMCR_RESET, BMCR_RESET);

+ isResetDone = true;

+}

+

+bool Tja1101_isResetComplete(EnetPhy_Handle hPhy)

+{

+ bool complete = false;

+

+ if(isResetDone)

+ {

+ ENETTRACE_DBG("PHY %u: reset is %scomplete\n", hPhy->addr, complete ? "" : "not");

+ isResetDone = false;

+ return true;

+ }

+ else

+ return complete;

+}

+

+static void Tja1101_printRegs(EnetPhy_Handle hPhy)

+{

+ uint32_t phyAddr = hPhy->addr;

+ uint16_t val = 0;

+ EnetPhy_readReg(hPhy, PHY_BMCR, &val);

+ EnetUtils_printf("PHY %u: BMCR = 0x%04x\n", phyAddr, val);

+ EnetPhy_readReg(hPhy, PHY_BMSR, &val);

+ EnetUtils_printf("PHY %u: BMSR = 0x%04x\n", phyAddr, val);

+ EnetPhy_readReg(hPhy, PHY_PHYIDR1, &val);

+ EnetUtils_printf("PHY %u: PHYIDR1 = 0x%04x\n", phyAddr, val);

+ EnetPhy_readReg(hPhy, PHY_PHYIDR2, &val);

+ EnetUtils_printf("PHY %u: PHYIDR2 = 0x%04x\n", phyAddr, val);

+}

diff --git a/psdkra/pdk_jacinto_10_01_00_25/packages/ti/drv/enet/src/phy/tja1101_priv.h b/psdkra/pdk_jacinto_10_01_00_25/packages/ti/drv/enet/src/phy/tja1101_priv.h

new file mode 100755

index 000000000..ab504a589

--- /dev/null

+++ b/psdkra/pdk_jacinto_10_01_00_25/packages/ti/drv/enet/src/phy/tja1101_priv.h

@@ -0,0 +1,94 @@

+/*

+ * Copyright (c) Texas Instruments Incorporated 2020

+ *

+ * Redistribution and use in source and binary forms, with or without

+ * modification, are permitted provided that the following conditions

+ * are met:

+ *

+ * Redistributions of source code must retain the above copyright

+ * notice, this list of conditions and the following disclaimer.

+ *

+ * Redistributions in binary form must reproduce the above copyright

+ * notice, this list of conditions and the following disclaimer in the

+ * documentation and/or other materials provided with the

+ * distribution.

+ *

+ * Neither the name of Texas Instruments Incorporated nor the names of

+ * its contributors may be used to endorse or promote products derived

+ * from this software without specific prior written permission.

+ *

+ * THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS

+ * "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT

+ * LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR

+ * A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT

+ * OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL,

+ * SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT

+ * LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE,

+ * DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY

+ * THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT

+ * (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE

+ * OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

+ */

+

+/*!

+ * \file tja1101_priv.h

+ *

+ * \brief This file contains private type definitions and helper macros for the

+ * TJA1101 Ethernet PHY.

+ */

+

+#ifndef TJA1101_PRIV_H_

+#define TJA1101_PRIV_H_

+

+/* ========================================================================== */

+/* Include Files */

+/* ========================================================================== */

+

+#include <stdint.h>

+#include "enetphy_priv.h"

+

+#ifdef __cplusplus

+extern "C" {

+#endif

+

+/* ========================================================================== */

+/* Macros */

+/* ========================================================================== */

+

+/* None */

+

+/* ========================================================================== */

+/* Structures and Enums */

+/* ========================================================================== */

+

+/* None */

+

+/* ========================================================================== */

+/* Global Variables Declarations */

+/* ========================================================================== */

+

+/* None */

+

+/* ========================================================================== */

+/* Function Declarations */

+/* ========================================================================== */

+

+/* None */

+

+/* ========================================================================== */

+/* Deprecated Function Declarations */

+/* ========================================================================== */

+

+/* None */

+

+/* ========================================================================== */

+/* Static Function Definitions */

+/* ========================================================================== */

+

+/* None */

+

+#ifdef __cplusplus

+}

+#endif

+

+#endif /* TJA1101_PRIV_H_ */

diff --git a/psdkra/vision_apps/utils/ethfw/src/app_ethfw_freertos.c b/psdkra/vision_apps/utils/ethfw/src/app_ethfw_freertos.c

index 063774c59..210e25868 100644

--- a/psdkra/vision_apps/utils/ethfw/src/app_ethfw_freertos.c

+++ b/psdkra/vision_apps/utils/ethfw/src/app_ethfw_freertos.c

@@ -166,9 +166,6 @@ static Enet_MacPort gEthAppPorts[] =

/* On J721E EVM to use all 8 ports simultaneously, we use below configuration

RGMII Ports - 1,3,4,8. QSGMII ports - 2,5,6,7 */

ENET_MAC_PORT_1, /* RGMII */

- ENET_MAC_PORT_3, /* RGMII */

- ENET_MAC_PORT_4, /* RGMII */

- ENET_MAC_PORT_8, /* RGMII */

#if defined(ENABLE_QSGMII_PORTS)

ENET_MAC_PORT_2, /* QSGMII main */

ENET_MAC_PORT_5, /* QSGMII sub */

@@ -210,104 +207,8 @@ static CpswAle_SetPolicerEntryInPartitionInArgs gEthApp_customPolicers[ETHFW_UTI

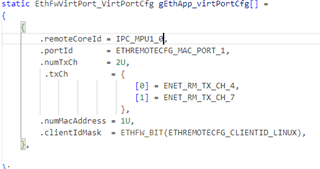

static EthFwVirtPort_VirtPortCfg gEthApp_virtPortCfg[] =

{

{

- .remoteCoreId = IPC_MPU1_0,

- .portId = ETHREMOTECFG_SWITCH_PORT_0,

-#if defined(ETHFW_EST_DEMO_SUPPORT) || defined(ETHFW_DEMO_SUPPORT)

- .numTxCh = 1U,

- .txCh = {

- [0] = ENET_RM_TX_CH_4

- },

-#else

- .numTxCh = 2U,

- .txCh = {

- [0] = ENET_RM_TX_CH_4,

- [1] = ENET_RM_TX_CH_7

- },

-#endif

- /* Number of rx flow for this virtual port */

- .numRxFlow = 1U,

- /* To create custom policers on rx flows clients need to give flow information (i.e. numCustomPolicers and customPolicersInArgs)

- * for each allocated flow.

- * Map the customPolicersInArgs with global custom policer's (i.e. gEthApp_customPolicers) array.

- * For example if numRxFlow is 1 and we want to create 1 custom policer to match with 2'nd custom policer in global array do this:

- * .rxFlowsInfo = {

- * [0] = {

- * .numCustomPolicers = 1U,

- * .customPolicersInArgs = {

- * [0] = &gEthApp_customPolicers[2U],

- * }

- * }

- * }

- * It is important to note that number of custom policers per rx flow is <= ETHREMOTECFG_POLICER_PERFLOW */

- .numMacAddress = 1U,

- .clientIdMask = ETHFW_BIT(ETHREMOTECFG_CLIENTID_LINUX) | ETHFW_BIT(ETHREMOTECFG_CLIENTID_QNX),

- },

- {

- .remoteCoreId = IPC_MCU1_0,

- .portId = ETHREMOTECFG_SWITCH_PORT_2,

- .numTxCh = 1U,

- .txCh = {

- [0] = ENET_RM_TX_CH_5,

- },

- .numRxFlow = 1U,

- .numMacAddress = 1U,

- .clientIdMask = ETHFW_BIT(ETHREMOTECFG_CLIENTID_AUTOSAR),

- },

- {

- /* Virtual switch port for Ethfw, using ETHREMOTECFG_SWITCH_PORT_LAST */

- .remoteCoreId = IPC_MCU2_0,

- .portId = ETHREMOTECFG_SWITCH_PORT_LAST,

-#if defined(ETHFW_EST_DEMO_SUPPORT) || defined(ETHFW_DEMO_SUPPORT)

- .numTxCh = 3U,

- .txCh = {

- [0] = ENET_RM_TX_CH_0,

- [1] = ENET_RM_TX_CH_7,

- [2] = ENET_RM_TX_CH_6

- },

-#else

- .numTxCh = 2U,

- .txCh = {

- [0] = ENET_RM_TX_CH_0,

- [1] = ENET_RM_TX_CH_6

- },

-#endif

- .numRxFlow = 5U,

- .numMacAddress = 1U,

- .clientIdMask = ETHFW_BIT(ETHREMOTECFG_CLIENTID_NONE),

- },

- {

- /* SWITCH_PORT_1 is used for both RTOS and Autosar client */

- .remoteCoreId = IPC_MCU2_1,

- .portId = ETHREMOTECFG_SWITCH_PORT_1,

- .numTxCh = 1U,

- .txCh = {

- [0] = ENET_RM_TX_CH_1

- },

- .numRxFlow = 1U,

- .numMacAddress = 1U,

- .clientIdMask = ETHFW_BIT(ETHREMOTECFG_CLIENTID_AUTOSAR) | ETHFW_BIT(ETHREMOTECFG_CLIENTID_RTOS),

- },

- {

- .remoteCoreId = IPC_MPU1_0,

- .portId = ETHREMOTECFG_MAC_PORT_1,

- .numTxCh = 1U,

- .txCh = {

- [0] = ENET_RM_TX_CH_3

- },

- .numRxFlow = 1U,

- .numMacAddress = 1U,

- .clientIdMask = ETHFW_BIT(ETHREMOTECFG_CLIENTID_LINUX) | ETHFW_BIT(ETHREMOTECFG_CLIENTID_QNX),

- },

- {

- .remoteCoreId = IPC_MCU2_1,

- .portId = ETHREMOTECFG_MAC_PORT_4,

- .numTxCh = 1U,

- .txCh = {

- [0] = ENET_RM_TX_CH_2

- },

- .numRxFlow = 1U,

- .numMacAddress = 1U,

- .clientIdMask = ETHFW_BIT(ETHREMOTECFG_CLIENTID_RTOS),

+ .remoteCoreId = IPC_MPU1_0,

+ .portId = ETHREMOTECFG_MAC_PORT_1,

},

};

@@ -990,7 +891,7 @@ static void EthApp_netifStatusCb(struct netif *netif)

appLogPrintf("Added interface '%c%c%d', IP is %s\n",

netif->name[0], netif->name[1], netif->num, ip4addr_ntoa(ipAddr));

-

+ appLogPrintf("ipaddr->addr=%d\n",ipAddr->addr);

if (ipAddr->addr != 0)

{

#if defined(ETHFW_DEMO_SUPPORT)

diff --git a/psdkra/vision_apps/utils/ethfw/src/concerto.mak b/psdkra/vision_apps/utils/ethfw/src/concerto.mak

index 9ba7f90ad..901d80e7c 100644

--- a/psdkra/vision_apps/utils/ethfw/src/concerto.mak

+++ b/psdkra/vision_apps/utils/ethfw/src/concerto.mak

@@ -64,7 +64,7 @@ ifeq ($(TARGET_OS),$(filter $(TARGET_OS),FREERTOS SAFERTOS))

else ifeq ($(ETHFW_INTERCORE_ETH_SUPPORT),yes)

DEFS += ETHAPP_ENABLE_INTERCORE_ETH

endif

- DEFS += ENABLE_QSGMII_PORTS

+ #DEFS += ENABLE_QSGMII_PORTS

endif

# iperf server support

--

2.34.1

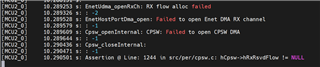

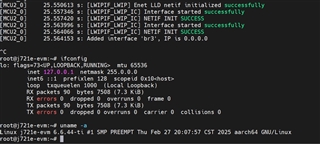

root@j721e-evm:~# /opt/vx_app_arm_remote_log.out |grep MCU2_0 [MCU2_0] 10.453853 s: CIO: Init ... Done !!! [MCU2_0] 10.453924 s: ### CPU Frequency = 1000000000 Hz [MCU2_0] 10.453964 s: CPU is running FreeRTOS [MCU2_0] 10.453985 s: APP: Init ... !!! [MCU2_0] 10.454006 s: SCICLIENT: Init ... !!! [MCU2_0] 10.454212 s: SCICLIENT: DMSC FW version [10.1.6--v10.01.06 (Fiery Fox)] [MCU2_0] 10.454255 s: SCICLIENT: DMSC FW revision 0xa [MCU2_0] 10.454283 s: SCICLIENT: DMSC FW ABI revision 4.0 [MCU2_0] 10.454309 s: SCICLIENT: Init ... Done !!! [MCU2_0] 10.454333 s: UDMA: Init ... !!! [MCU2_0] 10.455436 s: UDMA: Init ... Done !!! [MCU2_0] 10.455490 s: MEM: Init ... !!! [MCU2_0] 10.455525 s: MEM: Created heap (DDR_LOCAL_MEM, id=0, flags=0x00000004) @ e2400000 of size 15728640 bytes !!! [MCU2_0] 10.455583 s: MEM: Created heap (L3_MEM, id=1, flags=0x00000000) @ 3600000 of size 262144 bytes !!! [MCU2_0] 10.455629 s: MEM: Created heap (DDR_CACHE_WT_MEM, id=7, flags=0x00000000) @ e3300000 of size 1048576 bytes !!! [MCU2_0] 10.455684 s: MEM: Init ... Done !!! [MCU2_0] 10.455705 s: ETHFW: Init ... !!! [MCU2_0] 10.456715 s: ETHFW: Warning: Using 6 random MAC address(es) [MCU2_0] 10.456977 s: EnetMcm: CPSW_9G on MAIN NAVSS [MCU2_0] 10.465750 s: Mdio_open: MDIO manual mode enabled [MCU2_0] 10.465815 s: [MCU2_0] 10.466914 s: EnetUdma_openRxCh: RX flow alloc failed [MCU2_0] 10.466980 s: : -2 [MCU2_0] 10.467178 s: EnetHostPortDma_open: Failed to open Enet DMA RX channel [MCU2_0] 10.467231 s: : -1 [MCU2_0] 10.467263 s: Cpsw_openInternal: CPSW: Failed to open CPSW DMA [MCU2_0] 10.467298 s: : -1 [MCU2_0] 10.468089 s: Cpsw_closeInternal: [MCU2_0] 10.468130 s: : -1 [MCU2_0] 10.468157 s: Assertion @ Line: 1244 in src/per/cpsw.c: hCpsw->hRxRsvdFlow != NULL