- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

Tool/software:

hi,Team

I want to know how to implement M4F control epwm-SOCA pulse output function on AM620, but there is still no socA output.

Background:

ccs v12.8.1

development board: SK-AM62-LP

MCU + SDK AM62x_10_01_00_33

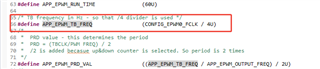

M4F project based on the epwm duty cycle in the example

Changes:

result

Speculation:

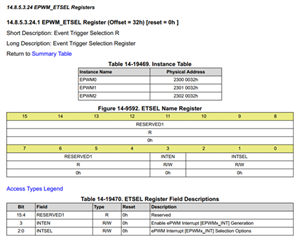

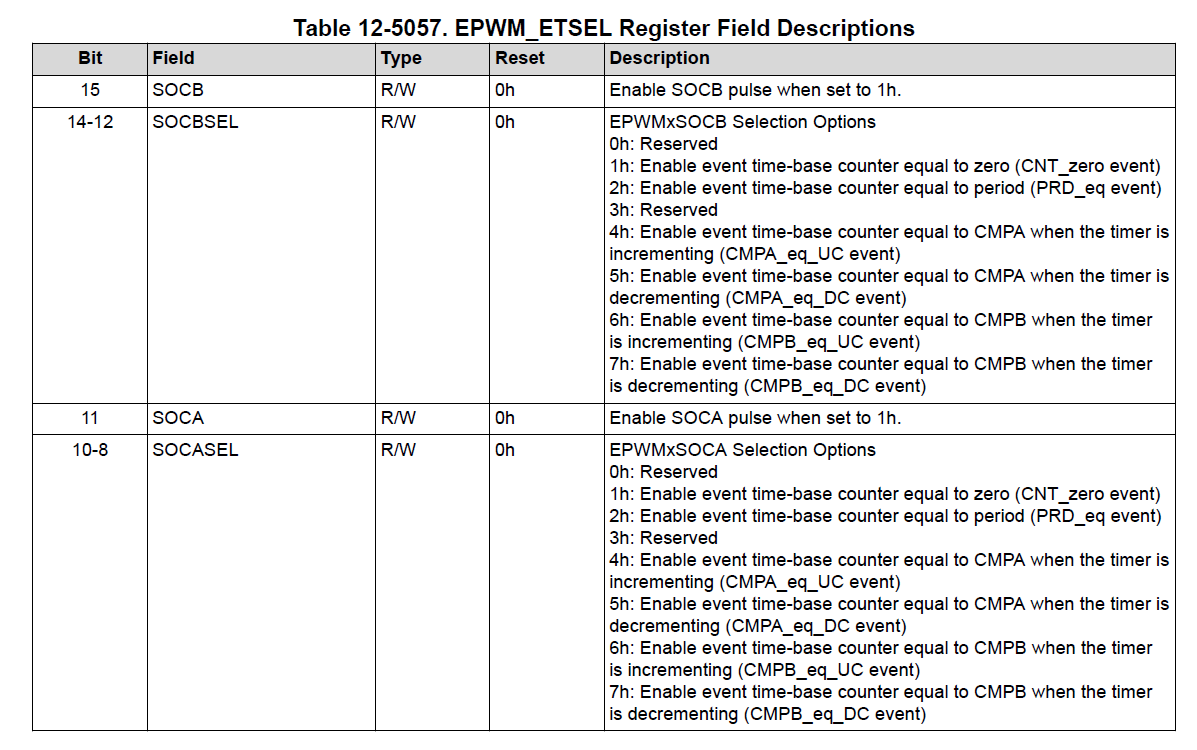

According to the description in TRM, there should be a dedicated bit for SOCASEL in EPWM_ETSEL, but there is no related bit in the description of the corresponding register in TRM, and no related input parameters are found in the API list. Please help clarify, thank you

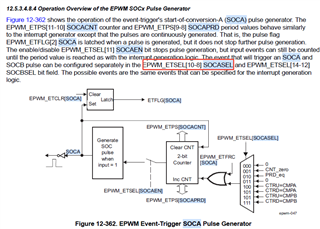

Hi, try the register bit settings below to control the SOC A and SOC B outputs.

The register description below belongs to the AM64X SOC and the PWM IPs are the same in the AM64X and AM62X device as well.

So, try to enable these bits and see if you are able to see the pulse on the SOCA and SOC B pin.

thank you

Paula

hi,Paula

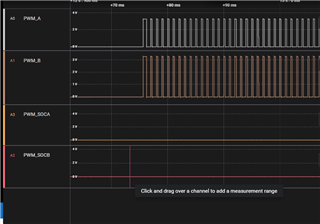

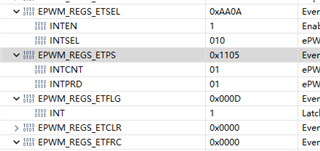

Modifying the ETSEL register alone with Jtag does not output the waveforms of soc A and socB.

I tried to modify the ETPS register at the same time,

the results were:

1. The pulse time of SOCA output is very short, about 200ns (epwm base clock is 250Mhz, divided by 4). This is too short for our application. I tried to modify the epwm division to 100, but the value remained unchanged.

My question is:

1. Can the pulse width of socA be adjusted? How to adjust it?

2. What does sysclk period mean in the TRM? If the pwm clock is 250Mhz and the frequency division is 4, what should the value of sysclk period be?