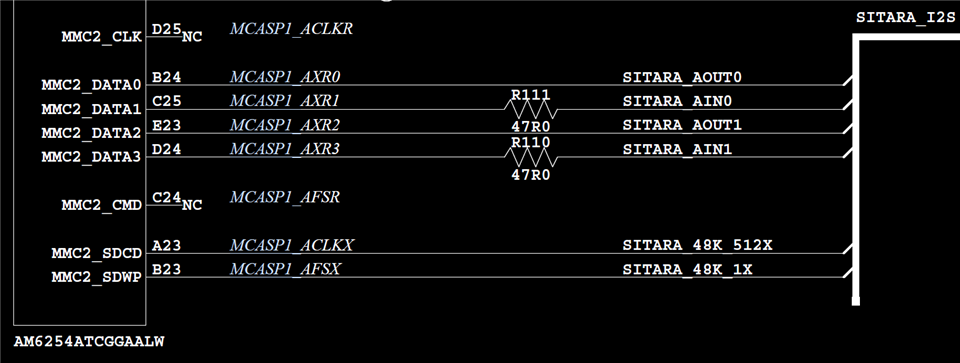

Part Number: AM625

Other Parts Discussed in Thread: PCM5102A, PCM5102, , SYSCONFIG

Tool/software:

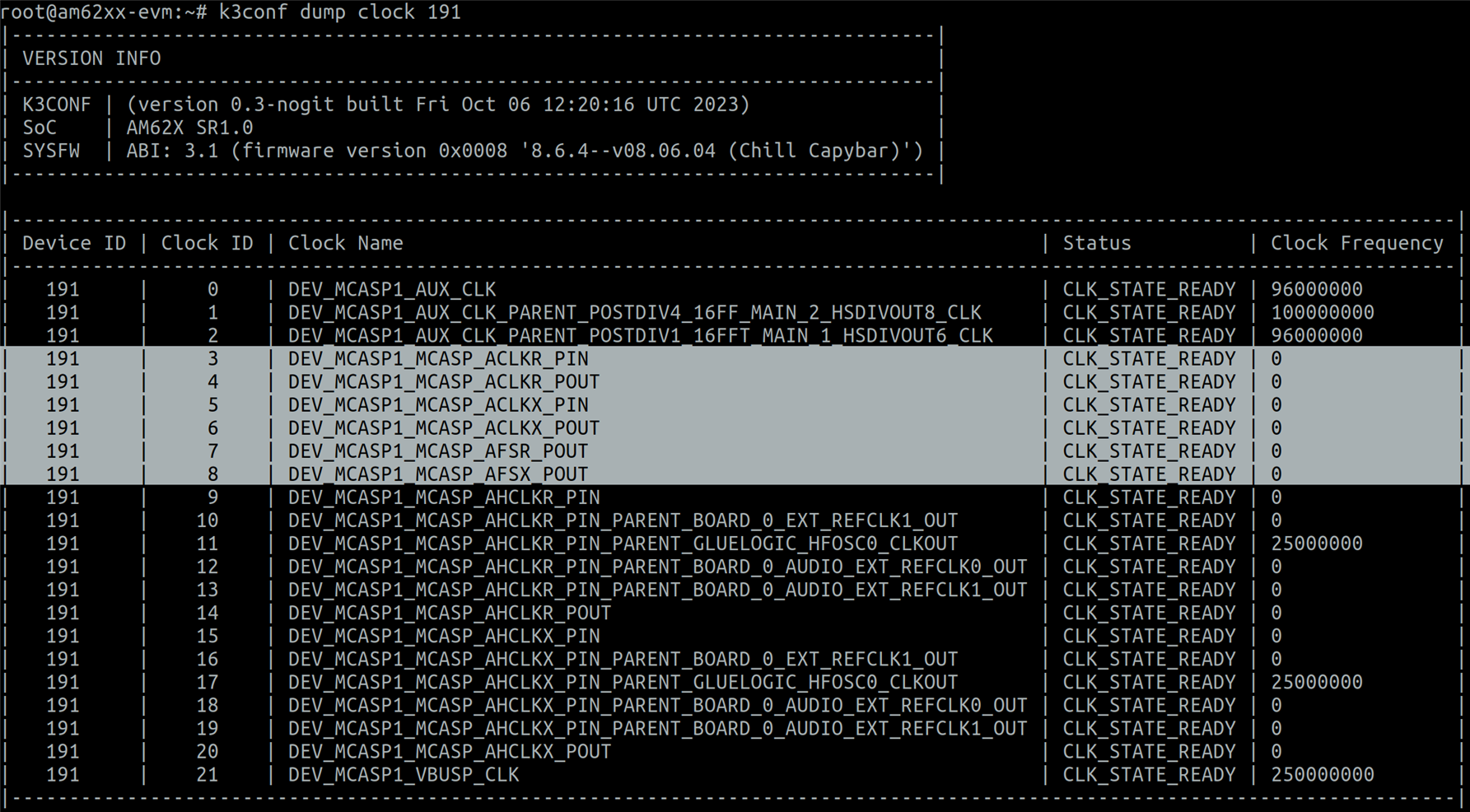

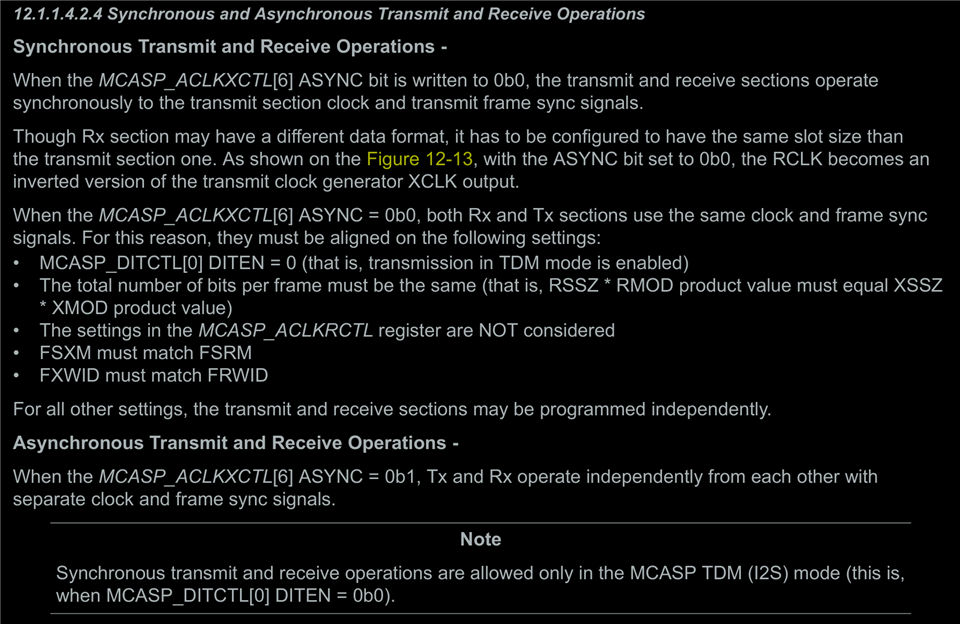

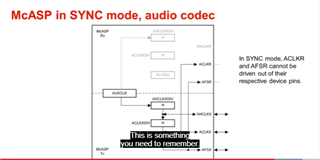

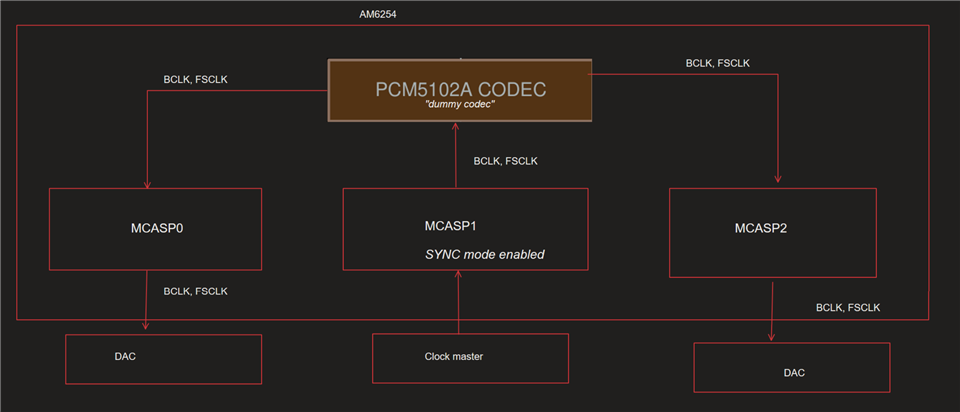

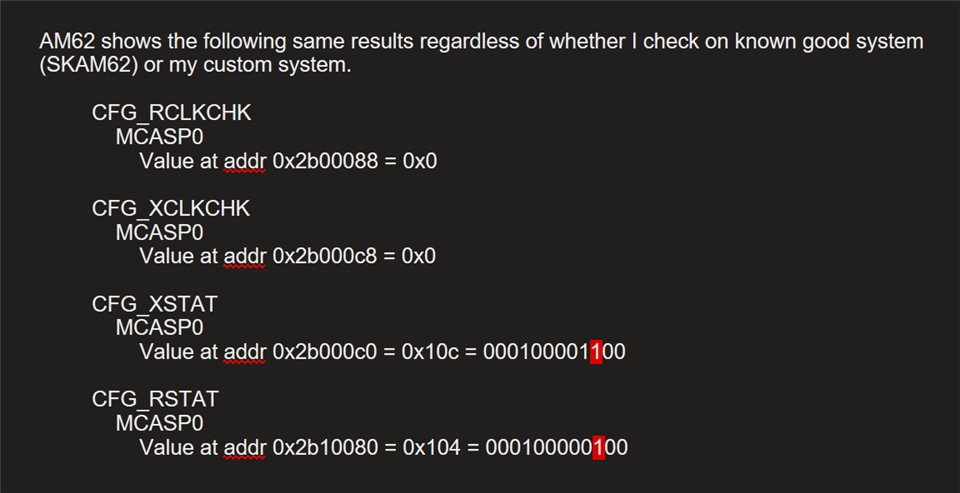

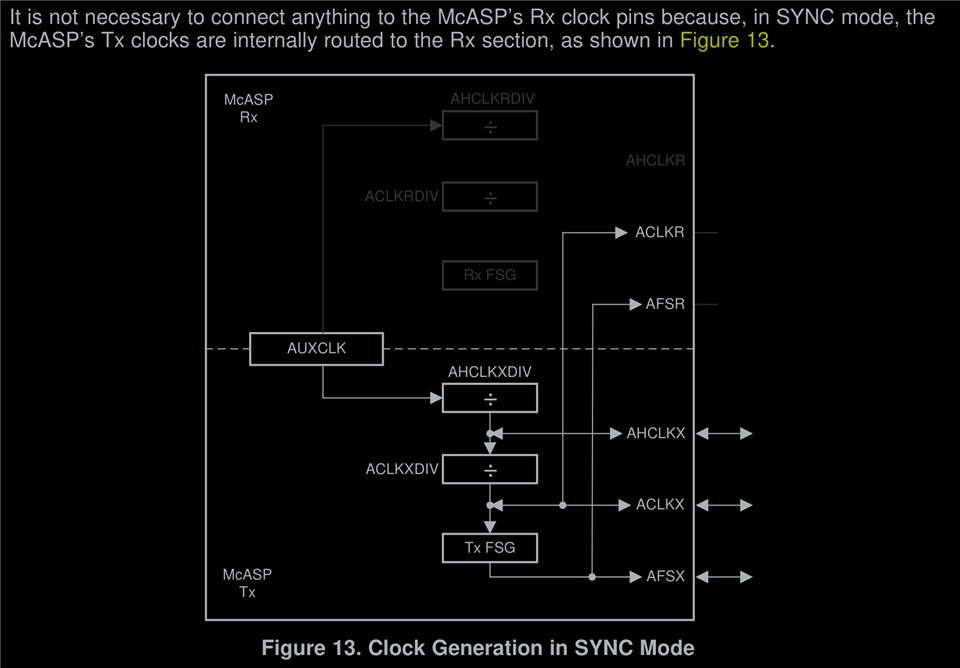

Main question: Is it possible to put AM6254 MCASP1 into Sync mode as described in section 4.3 (figure 13) of app note "SPRACK0 McASP Design Guide - Tips, Tricks, and Practical Examples"?

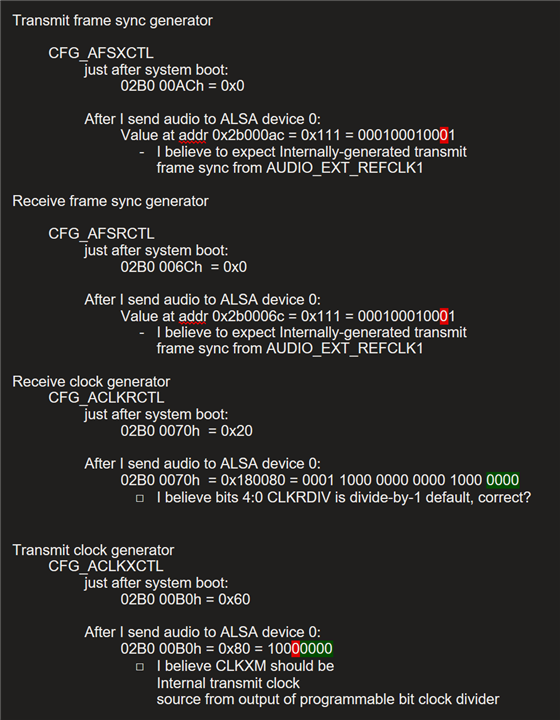

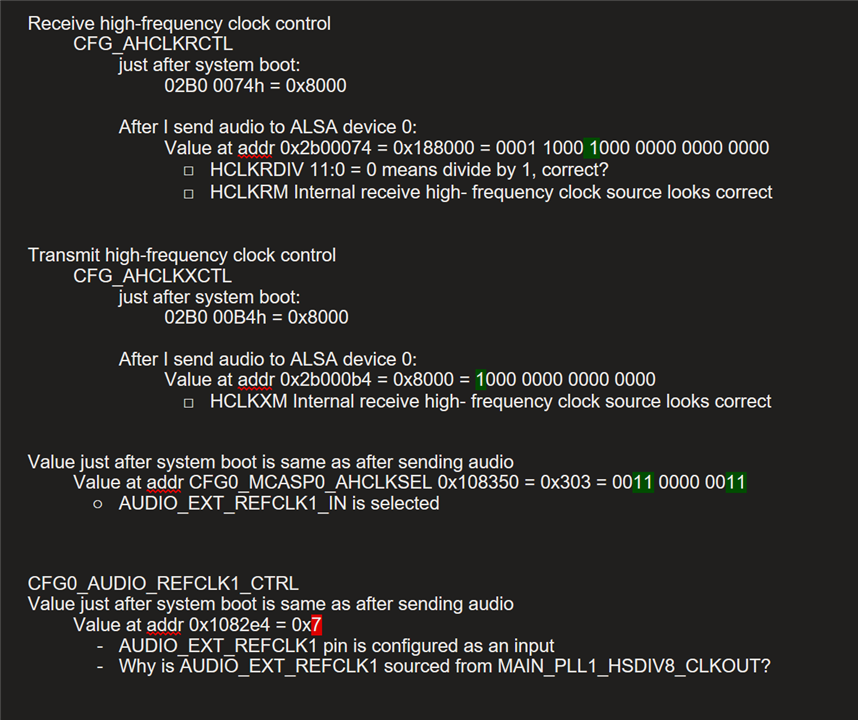

The app note says I can set this in ACLKXCTL, but looking at section 14.8.1.1.16.1 of TRM SPRUIV7B It's not clear if this is possible.

I'm using Linux TISDK v09.01.00.08.